Hi Siri/Others,

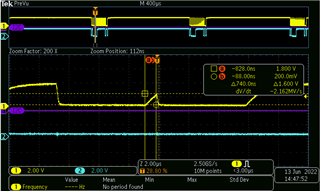

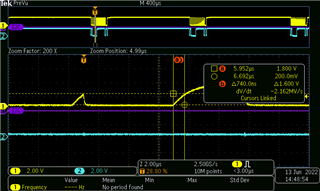

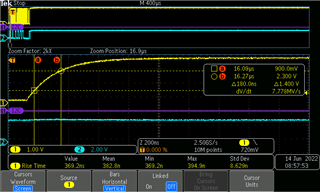

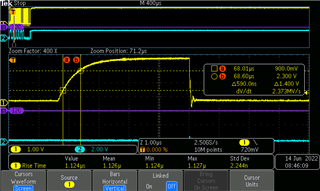

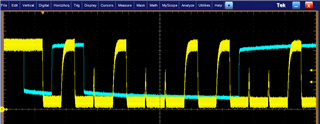

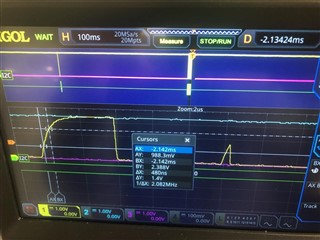

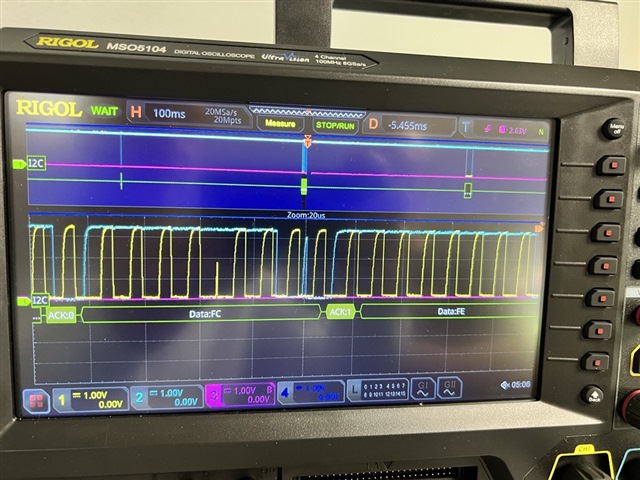

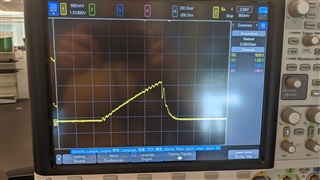

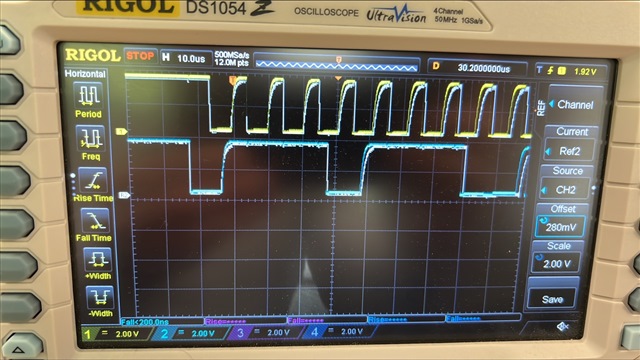

Several months ago when we were dealing with this clock runt issue, we slapped on a bandaid and kept moving, but now the problem has reared its head again in a way that we cannot bandaid. It appears to be related to capacitance on the bus. We can make it happen more frequently when we connect a beagle i2c protocol analyzer on the i2c. As was before, time is lost and the mcu appears to move on to the next clock pulse in the middle of the previous pulse. Instead of a full pulse, we just get a runt.

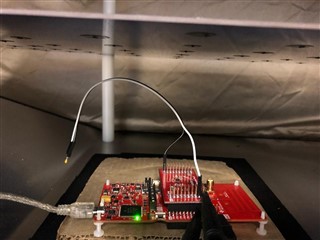

We think maybe this can be recreated by increasing bus capacitance. In investigating, we also noticed another strange phenomenon. When we add an additional sensor to the bus (Sensirion SPS30) or the beagle i2c protocol analyzer, the clock frequency slows down (not just changing the shape of the edge, actually pushing the pulses out so we get 99khz instead of 100khz for example). Since the clock is driven by the mcu, it is not clear why this would happen.

Could you please investigate and provide some insight into why these phenomena are occurring?

Thanks,

Scott