Other Parts Discussed in Thread: TIMAC, CC2650

Hello All,

I am unable to locate the Frontier tool, can some one guide where can i find the Frontier tool to configure the memory automatically.

I have an issue that my configuration uses ICALL_STACK0_ADDR as 0x9000.

My application image size has increased and would like to shift the stack image. If i change ICALL_STACK0_ADDR to anything else(say 0xA000). The application and stack images correctly gets loaded in the Flash at their respective configured addresses(stack = 0xA0000) however the Application and stack images doesn't interact.

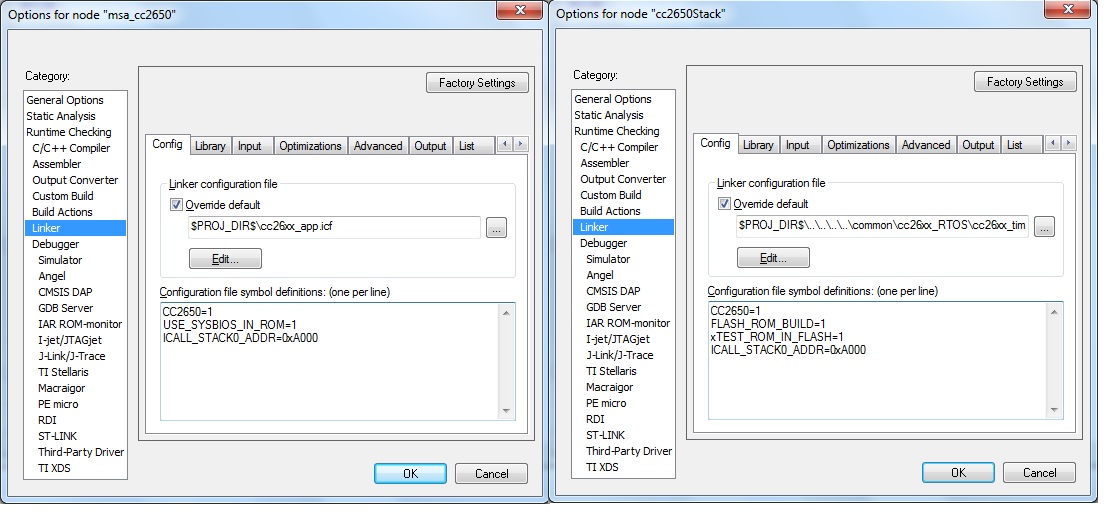

I have made the linker config settings for the application and stack as below:

Environment :CC26504xs custom board, IAR Workbench version - 7.40.2.8570, TIMAC - 1.5.2, TIRTOS - 2.11.01.09.

Am i missing anything here.

Please suggest.

Best regards

Naveen

This is how my cc26xx_timac_stack_release.icf looks like:

/*******************************************************************************

Filename: cc26xx_timac_stack.icf

Revised: $Date: 2014-05-14 14:50:19 -0700 (Wed, 14 May 2014) $

Revision: $Revision: 38545 $

Description: IAR ARM Linker Configuration File - BLE Stack

Note: Code stack and heap are allocated by the Application/RTOS build.

Imported Symbols

Note: Linker defines are located in the IAR IDE project using --config_def

in Options->Linker->Extra Options, or placed in Options->Linker->

Config->Configuration file symbol definitions.

CCxxxx: Device Name (e.g. CC2650).

FLASH_ONLY_BUILD: Build full TIMAC stack in flash only memory.

FLASH_ROM_BUILD: Build Flash portion of TIMAC stack to work with ROM code.

ROM_BUILD: Build ROM portion of TIMAC stack.

COMMON_ROM_BUILD: Build of common ROM code.

TEST_ROM_IN_FLASH: Build ROM code in Flash memory to test.

ICALL_STACK0_ADDR: Start address of flash only and flash ROM builds.

ICALL_RAM0_ADDR: Start address of RAM.

Exported Symbols

Note: Can be used as externs in C code.

ROM_BASE_ADDR: Location of start of ROM (where RT Init is expected).

RAM_BASE_ADDR: Location of start of RAM (for ICall and JT pointers).

COMMON_RAM_BASE_ADDR: Location of start of RAM (for ICall and JT pointers).

PAGE_SIZE: Size of Flash sector, in bytes.

NUM_SNV_PAGES: Number of sectors used for Simple NV.

Copyright 2013-2014 Texas Instruments Incorporated. All rights reserved.

IMPORTANT: Your use of this Software is limited to those specific rights

granted under the terms of a software license agreement between the user

who downloaded the software, his/her employer (which must be your employer)

and Texas Instruments Incorporated (the "License"). You may not use this

Software unless you agree to abide by the terms of the License. The License

limits your use, and you acknowledge, that the Software may not be modified,

copied or distributed unless embedded on a Texas Instruments microcontroller

or used solely and exclusively in conjunction with a Texas Instruments radio

frequency transceiver, which is integrated into your product. Other than for

the foregoing purpose, you may not use, reproduce, copy, prepare derivative

works of, modify, distribute, perform, display or sell this Software and/or

its documentation for any purpose.

YOU FURTHER ACKNOWLEDGE AND AGREE THAT THE SOFTWARE AND DOCUMENTATION ARE

PROVIDED “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED,

INCLUDING WITHOUT LIMITATION, ANY WARRANTY OF MERCHANTABILITY, TITLE,

NON-INFRINGEMENT AND FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL

TEXAS INSTRUMENTS OR ITS LICENSORS BE LIABLE OR OBLIGATED UNDER CONTRACT,

NEGLIGENCE, STRICT LIABILITY, CONTRIBUTION, BREACH OF WARRANTY, OR OTHER

LEGAL EQUITABLE THEORY ANY DIRECT OR INDIRECT DAMAGES OR EXPENSES

INCLUDING BUT NOT LIMITED TO ANY INCIDENTAL, SPECIAL, INDIRECT, PUNITIVE

OR CONSEQUENTIAL DAMAGES, LOST PROFITS OR LOST DATA, COST OF PROCUREMENT

OF SUBSTITUTE GOODS, TECHNOLOGY, SERVICES, OR ANY CLAIMS BY THIRD PARTIES

(INCLUDING BUT NOT LIMITED TO ANY DEFENSE THEREOF), OR OTHER SIMILAR COSTS.

Should you have any questions regarding your right to use this Software,

contact Texas Instruments Incorporated at www.TI.com.

*******************************************************************************/

////////////////////////////////////////////////////////////////////////////////

// Memory Sizes

////////////////////////////////////////////////////////////////////////////////

////////////////////////////////////////////////////////////////////////////////

// Chameleon

if ( isdefinedsymbol(CC2650) )

{

define symbol RAM_SIZE = 0x00005000; // 20K

define symbol FLASH_SIZE = 0x00020000; // 128K

define symbol ROM_SIZE = 0x0001C000; // 115K

}

////////////////////////////////////////////////////////////////////////////////

// Default

else

{

define symbol RAM_SIZE = 0x00004000; // 16K

define symbol FLASH_SIZE = 0x00020000; // 128K

define symbol ROM_SIZE = 0x00018000; // 96K

}

////////////////////////////////////////////////////////////////////////////////

// Memory Definitions

////////////////////////////////////////////////////////////////////////////////

////////////////////////////////////////////////////////////////////////////////

// CM3 FW

//

define symbol FW_START = 0x10000000;

define symbol FW_END = 0x10004BFF;

define symbol FLASH_END_MODIFY = 0x1BFFF;

////////////////////////////////////////////////////////////////////////////////

// ROM

//

if ( isdefinedsymbol(COMMON_ROM_BUILD) )

{

if ( isdefinedsymbol(TEST_ROM_IN_FLASH) )

{

define symbol ROM_START = 0x0001A000;

define symbol ROM_END = 0x0001EFFF;

}

else // ROM code is in ROM memory

{

define symbol ROM_START = 0x10014C00;

define symbol ROM_END = 0x10019FFF;

}

}

else if ( isdefinedsymbol(ROM_BUILD) )

{

if ( isdefinedsymbol(TEST_ROM_IN_FLASH) )

{

define symbol ROM_START = 0x00010000;

define symbol ROM_END = 0x00019FFF;

}

else // ROM code is in ROM memory

{

define symbol ROM_START = 0x1000E000;

define symbol ROM_END = 0x10014BFF;

}

}

else // not a ROM build

{

define symbol ROM_START = 0x00010000;

define symbol ROM_END = 0x0001FFFF;

}

// export the ROM base address

if ( isdefinedsymbol(ROM_BUILD) || isdefinedsymbol(COMMON_ROM_BUILD) )

{

define symbol ROM_BASE_ADDR = ROM_START+1;

export symbol ROM_BASE_ADDR;

}

////////////////////////////////////////////////////////////////////////////////

// RAM

//

if ( isdefinedsymbol(FLASH_ONLY_BUILD) )

{

if ( isdefinedsymbol(ICALL_RAM0_ADDR) )

{

define symbol RAM_START = ICALL_RAM0_ADDR;

}

else // default

{

define symbol RAM_START = 0x20002A00;

}

if ( isdefinedsymbol(CC2650) )

{

define symbol RAM_END = 0x20004FFF;

}

else // default

{

define symbol RAM_END = 0x20003FFF;

}

}

else if ( isdefinedsymbol(COMMON_ROM_BUILD) )

{

if ( isdefinedsymbol(CC2650) )

{

define symbol RAM_START = 0x20004F2C;

define symbol RAM_END = 0x20004FFF;

}

else // default

{

define symbol RAM_START = 0x20003200;

define symbol RAM_END = 0x200032FF;

}

define symbol COMMON_RAM_BASE_ADDR = RAM_START;

export symbol COMMON_RAM_BASE_ADDR;

}

else if ( isdefinedsymbol(ROM_BUILD) )

{

if ( isdefinedsymbol(CC2650) )

{

define symbol RAM_START = 0x20004A14;

define symbol RAM_END = 0x20004EFF;

}

else

{

define symbol RAM_START = 0x20003300;

define symbol RAM_END = 0x20003FFF;

}

define symbol RAM_BASE_ADDR = RAM_START;

export symbol RAM_BASE_ADDR;

}

else if ( isdefinedsymbol(FLASH_ROM_BUILD) )

{

if ( isdefinedsymbol(CC2650) )

{

if ( isdefinedsymbol(ICALL_RAM0_ADDR) )

{

define symbol RAM_START = ICALL_RAM0_ADDR;

}

else

{

define symbol RAM_START = 0x20004200;

}

define symbol RAM_END = 0x20004FFF;

}

else

{

if ( isdefinedsymbol(ICALL_RAM0_ADDR) )

{

define symbol RAM_START = ICALL_RAM0_ADDR;

}

else

{

define symbol RAM_START = 0x20002A00;

}

define symbol RAM_END = 0x200031FF;

}

}

else // unknown build

{

define symbol RAM_START = 0xFFFFFFFF;

define symbol RAM_END = 0xFFFFFFFF;

}

////////////////////////////////////////////////////////////////////////////////

// Flash

//

define symbol PAGE_SIZE = 0x1000;

export symbol PAGE_SIZE;

define symbol NUM_RESERVED_PAGES = 1;

define symbol RESERVED_SIZE = (NUM_RESERVED_PAGES * PAGE_SIZE);

define symbol NUM_SNV_PAGES = 2;

export symbol NUM_SNV_PAGES;

define symbol SNV_SIZE = (NUM_SNV_PAGES * PAGE_SIZE);

define symbol SNV_START = (FLASH_SIZE - (RESERVED_SIZE + SNV_SIZE));

define symbol SNV_END = (SNV_START + SNV_SIZE - 1);

if ( isdefinedsymbol(FLASH_ONLY_BUILD) )

{

if ( isdefinedsymbol(ICALL_STACK0_ADDR) )

{

define symbol FLASH_START = ICALL_STACK0_ADDR;

}

else // default

{

define symbol FLASH_START = 0x0000A000;

}

define symbol FLASH_END = (SNV_START - 1);

}

else if ( isdefinedsymbol(ROM_ONLY_BUILD) || isdefinedsymbol(COMMON_ROM_BUILD) )

{

define symbol FLASH_START = ROM_START;

define symbol FLASH_END = ROM_END;

}

else if ( isdefinedsymbol(FLASH_ROM_BUILD) )

{

if ( isdefinedsymbol(ICALL_STACK0_ADDR) )

{

define symbol FLASH_START = ICALL_STACK0_ADDR;

}

else // default

{

define symbol FLASH_START = 0x0000A000;

}

if ( isdefinedsymbol(TEST_ROM_IN_FLASH) )

{

define symbol FLASH_END = (ROM_START-1);

}

else // ROM code is in ROM memory

{

// define symbol FLASH_END = FLASH_END_MODIFY ;

define symbol FLASH_END = (0x10000 -1);

}

}

else // unknown build

{

define symbol FLASH_START = 0xFFFFFFFF;

define symbol FLASH_END = 0xFFFFFFFF;

}

////////////////////////////////////////////////////////////////////////////////

// ROM Revision Number

//

if ( isdefinedsymbol(ROM_BUILD) || isdefinedsymbol(COMMON_ROM_BUILD) )

{

define symbol ROM_CRC_SIZE = 2;

define symbol ROM_REV_SIZE = 2;

define symbol ROM_REV_START = ROM_END - (ROM_CRC_SIZE + 1);

define symbol ROM_REV_END = ROM_REV_START + ROM_REV_SIZE - 1;

}

////////////////////////////////////////////////////////////////////////////////

// Memory Regions

////////////////////////////////////////////////////////////////////////////////

define memory mem with size = 4G;

define region FW = mem:[from FW_START to FW_END];

define region ROM = mem:[from ROM_START to ROM_END];

define region FLASH = mem:[from FLASH_START to FLASH_END];

define region RAM = mem:[from RAM_START to RAM_END];

define region SNV_FLASH = mem:[from SNV_START to SNV_END];

if ( isdefinedsymbol(ROM_BUILD) || isdefinedsymbol(COMMON_ROM_BUILD) )

{

define region ROM_REV = mem:[from ROM_REV_START to ROM_REV_END];

}

////////////////////////////////////////////////////////////////////////////////

// Flash Software Entry Point

////////////////////////////////////////////////////////////////////////////////

if ( isdefinedsymbol(FLASH_ONLY_BUILD) || isdefinedsymbol(FLASH_ROM_BUILD) )

{

place at start of FLASH { readonly section EntrySection };

}

////////////////////////////////////////////////////////////////////////////////

// Memory Placement

// For ROM: C Runtime, Checksum, ROM Revision Number, Flash JT, and FPB.

////////////////////////////////////////////////////////////////////////////////

if ( isdefinedsymbol(ROM_BUILD) || isdefinedsymbol(COMMON_ROM_BUILD) )

{

place in ROM { readonly };

place in RAM { readwrite };

// ROM C Runtime Routine

place at start of ROM { ro section .romRuntimeInit };

keep { section .romRuntimeInit };

// Checksum

place at end of ROM { ro section .checksum };

keep { section .checksum };

// ROM Revision Number

place at start of ROM_REV { ro section .rom_rev };

keep { section .rom_rev };

// ICall Functions and R2F and R2R Flash Jump Table Location Pointers

place at start of RAM { section .ramInitTable };

keep { section .ramInitTable };

}

else // !ROM_BUILD && !COMMON_ROM_BUILD

{

place in FLASH { readonly };

place in RAM { readwrite };

// Simple NV

define block .snv_mem with size=SNV_SIZE, alignment=4 { ro section .snv_mem };

place at start of SNV_FLASH { block .snv_mem };

keep { ro section .snv_mem };

}

////////////////////////////////////////////////////////////////////////////////

// Initialization

////////////////////////////////////////////////////////////////////////////////

if ( isdefinedsymbol(ROM_BUILD) || isdefinedsymbol(COMMON_ROM_BUILD) )

{

initialize by copy { readwrite };

}

else

{

initialize by copy with packing = packbits { readwrite };

}

do not initialize

{

section .noinit,

section .stack,

};

////////////////////////////////////////////////////////////////////////////////