Dears

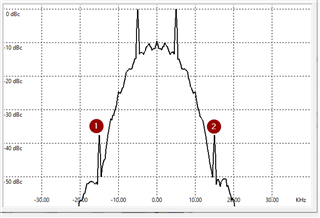

During the GS529p07 & P08 EMC test, the customer found that: adjacent channel power.

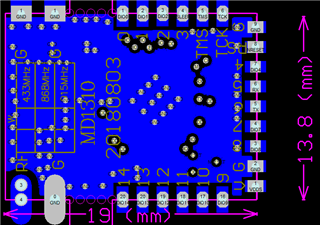

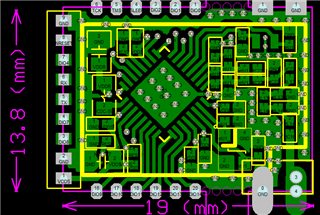

Please help check whether there are configuration and PCB problems. Thank you very much!

Design application: smoke alarm

PN:CC1310

CC1310 Adjacent channel power issue by 433MHZ

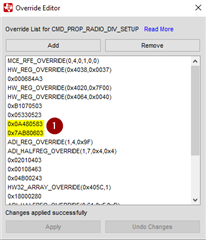

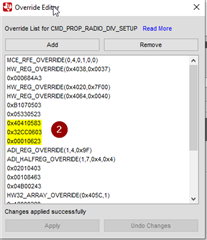

The following is our software configuration:

pcblayout a and b

GS529-P07 Waveform&Report:

NC letter report (2020-3-10)--EMC format GFT-OP-10a Letter Report_GZ.pdf