Other Parts Discussed in Thread: SYSBIOS,

Hello,

I have 2 designs, one will incorporate the use of the bootloader (has external EEPROM), and another design that will not need require a bootloader (No external EEPROM or UART connection). I'm trying to understand the entire bootloader process and how it works within the TI RTOS Eco-System.

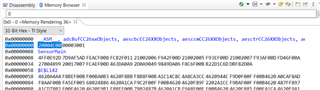

The processor exception address location starts at address 0x00000000 - 0x03C (exceptions). I see that the system creates a structure of ti_sysbios_family_arm_m3_Hwi_resetVectors which is placed at 0x2000 (see pic below) which has what appears to look like that right structure but should reside at address 0x0 instead of 0x2000 as shown below? It is setup properly as that location of 0x2000 but what I have at 0x0 is random code that is starting 0x00 which is wrong. It works fine in a debugger but doesn't run from POR when not connected to a debugger. I'm trying to find the correct configuration to:

1. bypass the bootloader for one design. (Project A)

2. Incorporate the bootloader for one design. (Project B)

3. create the proper *.CMD file to facilitate the memory map such that #1 & #2 can be created.

4. create the proper *.cfg file to facilitate the memory map such that #1 & #2 can be created.

Please note these are separate projects and will have different files that are unique to that project.

Thank you,

Shawn