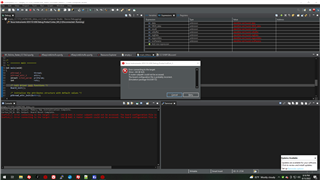

I have develop a custom board with the CC1310F128RGZ and CC1312 as the debugger and programmer. I am using the "empty" project to do some initial tests, but I am experiencing a problem where the code only seems to run while in debug mode and manually stepping (F6) though the code with breakpoints. If i remove the breakpoints and continue even in debug, the code does not run. The code does not seem to run even when exiting out of debugging.

I have set LF XTAL to #define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x3// LF RCOSC and this does not seem to fix the issues.

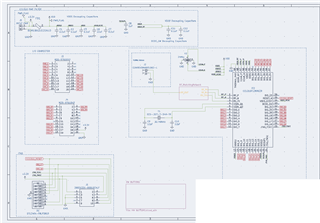

Also my custom board is built referencing the C1310 LP Schematic and PCB Design Guidelines. Below is an image of the schematic of the custom board