Other Parts Discussed in Thread: CC1352R, SYSCONFIG

Hello,

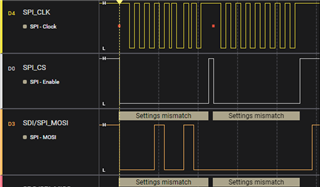

I am trying to communicate via SPI. I have started with the SPI Master Example (spimaster_CC1312R1_LAUNCHXL_tirtos_ticlang) and tried to modify it so that it fit my needs. But I can't get it to work properly, the CS line get's deasserted after every byte. But I need the CS line low for the duration of the transaction. How do I achieve this?

The Waveform look like this.

Frame Format: SPI mode Polarity 0 Phase 1

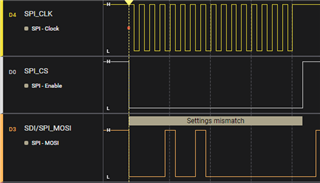

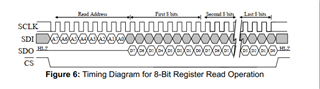

But I need it like this:

Here: CS is low for the duration of the read operation (transaction?) And thats what I need.

I tried all spi frame formats:

- SPI mode Polarity 0 Phase 0

- SPI mode Polarity 0 Phase 1

- SPI mode Polarity 1 Phase 0

- SPI mode Polarity 1 Phase 1

- TI mode

- Micro-wire mode

with no success.

I am using:

- CCS 12

- TI RTOS

- CC1352R

- CC13x2 SDK

Thanks in advance and

Kind regards