Hello,

I have a product using the CC1352 MCU. During production I need to test the PCB components by applying voltages on some nets, these nets sometimes are connected directly to the MCU GPIOs while the board is powered off.

The questions are:

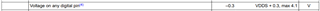

- What is the state of the MCU GPIOS when it's not powered? Are they in high impedance state?

- Is it safe to apply a voltage on powered off MCU? If not, then what's the recommended approach?

Thanks.