Hi,

Have the following issue:

Our product is using 2 CC1121 radio's working on the same channel (frequency).

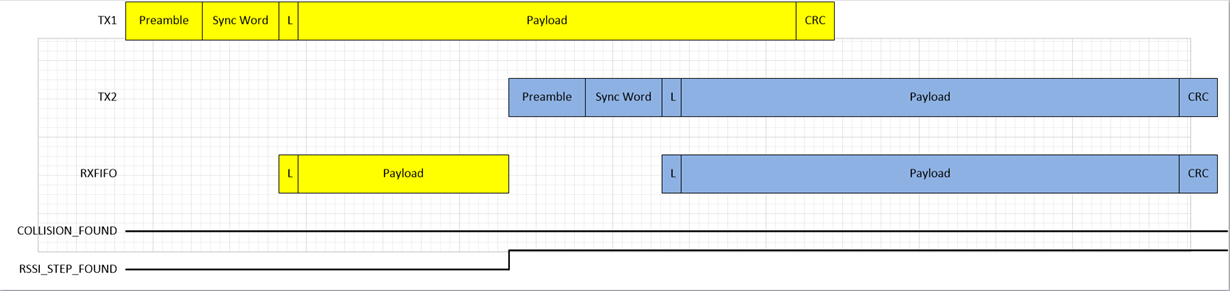

Our product is sending a beacon message every few mSec on Radio 2, while the other radio continue to RX.

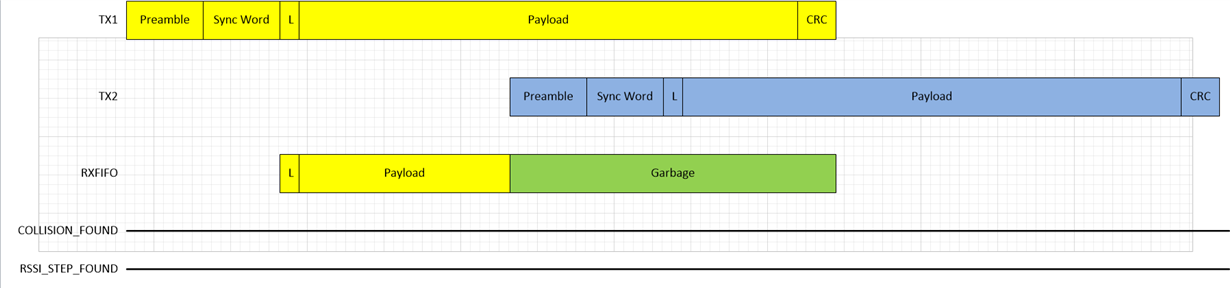

In some scenario, a valid data is arriving and fetched into Radio1 FIFO. Radio2 is sending a beacon data (with higher signal strength) and the data is overwriting the valid data.

I would expected to get:

1. CRC error (in most cases indeed we are getting it)

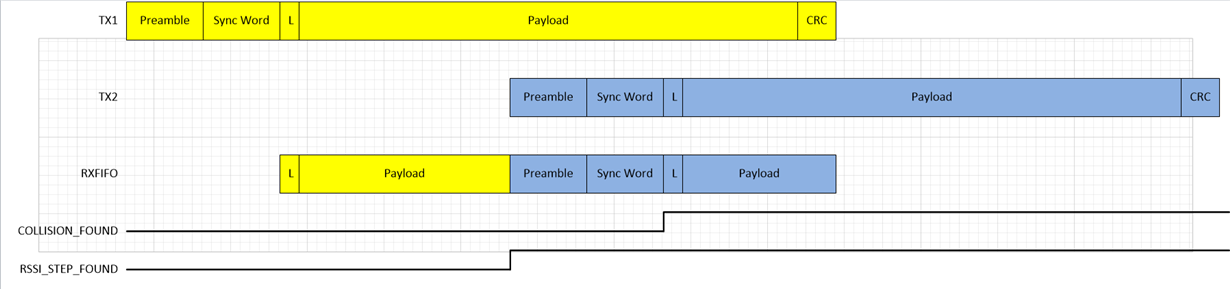

2. Collision found signal, as the beacon sync word is inserted while a valid packet is received.

However, we are not getting the collision indication. (MDMCFG1 = 0x4E).

We don't have the option to get an interrupt on the collision (relevant gpio is not connected), but just read the flag from register DEM_STATUS when validate the received packet.

What is the exact scenario of collision?

what is the trigger for the flag in DEM_STATUS to reset (maybe I'm reading it too late)?

Currently a garbage data is enter into our system.

Thanks,

Dagan