Other Parts Discussed in Thread: CC1101,

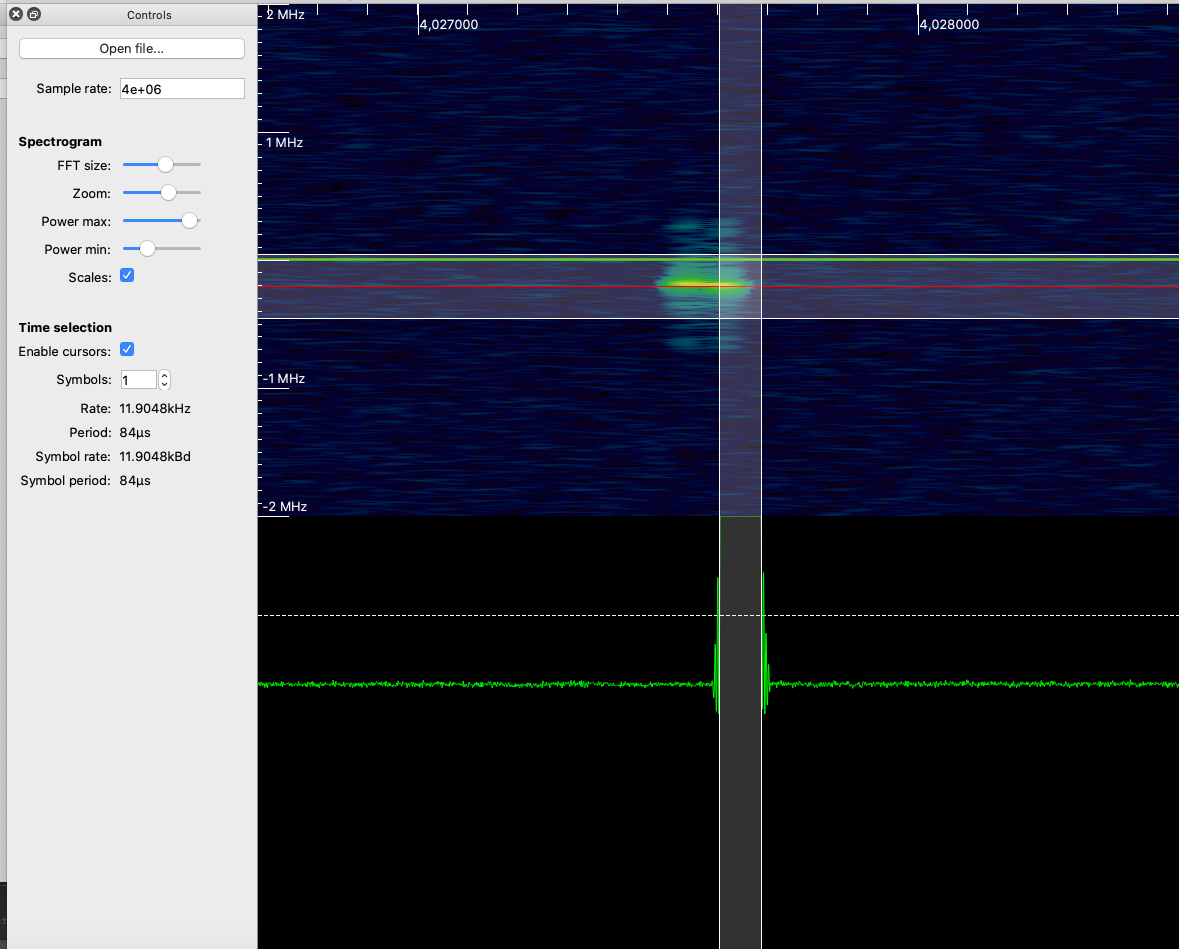

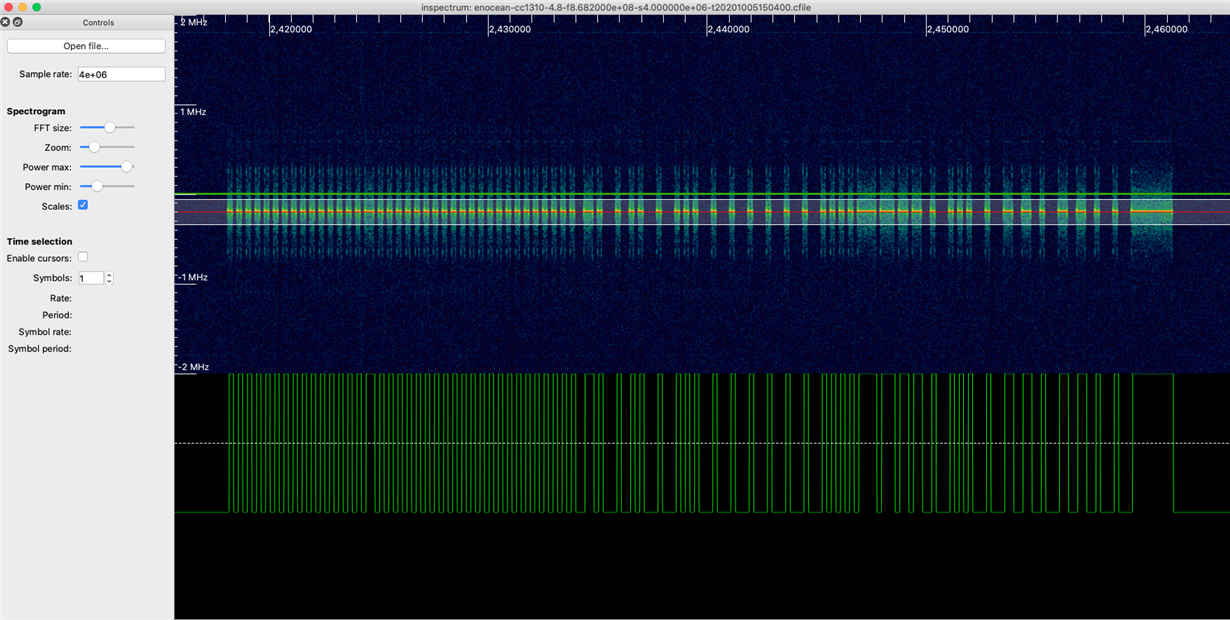

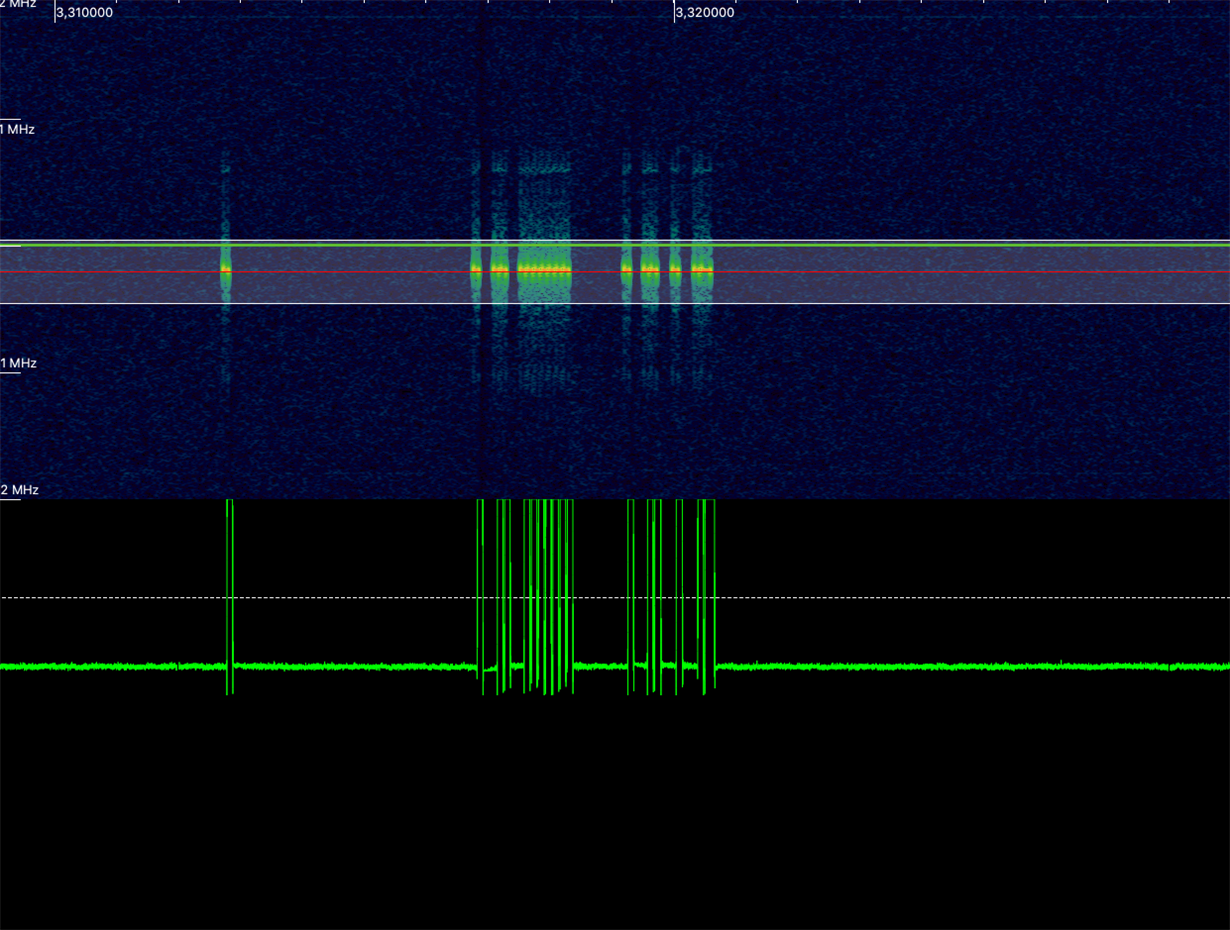

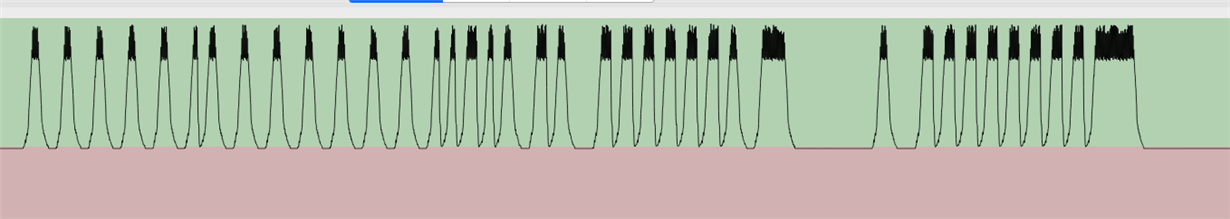

We are developing window contacts and sensors to detects the position of the window handle. For one of our customers we need to transmit EnOcean packets. The EnOcean packets must be ASK(OOK) modulated with a bitrate of 125kbit/s.

We can transmit these types of packets with a CC1101 easily, but with the CC1310 it is not possible.

Do we have to use a different transceiver for this or is there any chance to transmit these packets with a CC1310?

We only have to transmit these packets - receiving is not necessary!