Dear all,

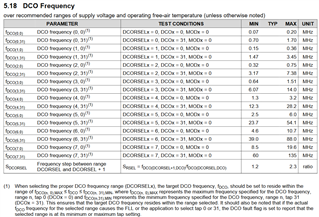

Some of devices (ca 6%) from 91K AD34 lot would not start at low temperature (<10°C). It seems that the 4MHz FLL doesn`t oscillate. At temperature over 20°C the device/application works well. Processor is in our application over 10 years, without problems. No changes in Firmware, HW or production line have been done in the meantime.

I need to find out the root cause for this defect, urgently.

Thank You.