Other Parts Discussed in Thread: SYSCONFIG

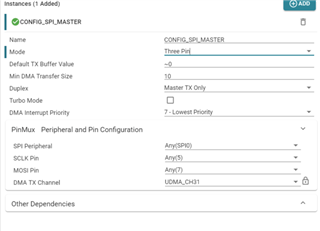

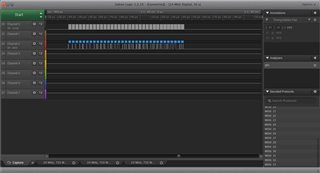

I have been able to successfully transfer data using spi if I set the minimum DMA bytes to something really high, however when I set the min dma transfer size to something smaller as shown in the picture, I keep running into dmaErrorFxn at run time.

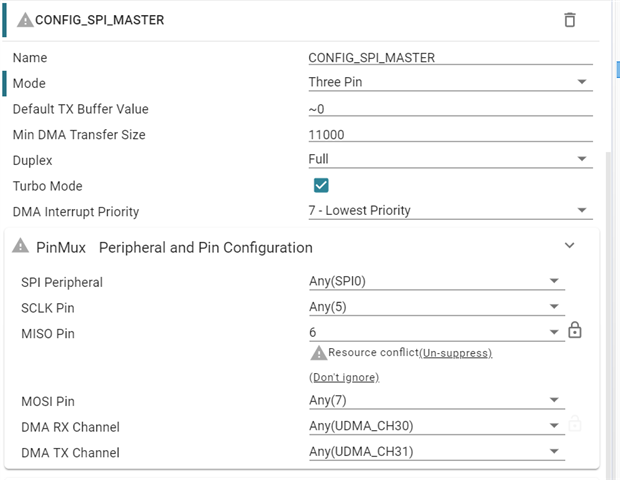

My current spi configurations are shown below:

I would like some help debugging this.

Thanks!

Vasav

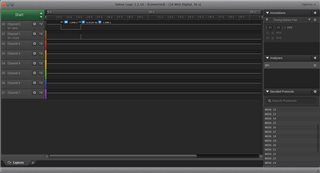

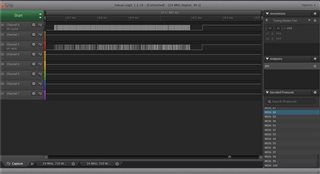

As you can see, only 33 bytes are sent and after that it gets stuck in the freeRTOS stuff.

As you can see, only 33 bytes are sent and after that it gets stuck in the freeRTOS stuff.