Other Parts Discussed in Thread: UNIFLASH, ,

Hello,

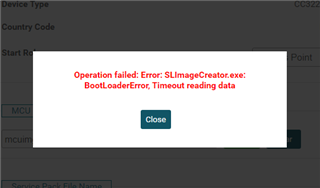

We have designed a custom board by using CC3220S chip. When firmware loading through UART pins it shows the error, "BootLoaderError, Timeout Reading the data". I followed the CC3220S Launchpad design files and CC3220 Prduction Line guide user manual for my design.

For Firmware loading pin connections are Lunch Pad XDS110 UART TX connected to CC3220S RX(57), XDS110 RX line to CC3220S TX(55) , XDS Reset Pin to CC3220S nReset(32) and also make ground line common. The SOP0 ,SOP1 and SOP2 settings are Low,Low,High combination used for firmware loading.

Questions are

1. Do we need to load any bootloader firmware initially to the chip ?

2. Any issues when Fresh SPI flash chip used?

3. Do i need to use any other PINS (UART TX,RX,nRESET,SOP0,SOP1,SOP2, GND and 3.3V) for programming the chip?

4. Is it possible to verify my Hardware files from your team?

Thank you for your Support in advance.

Abhilash Job