Other Parts Discussed in Thread: WL1831

Hello,

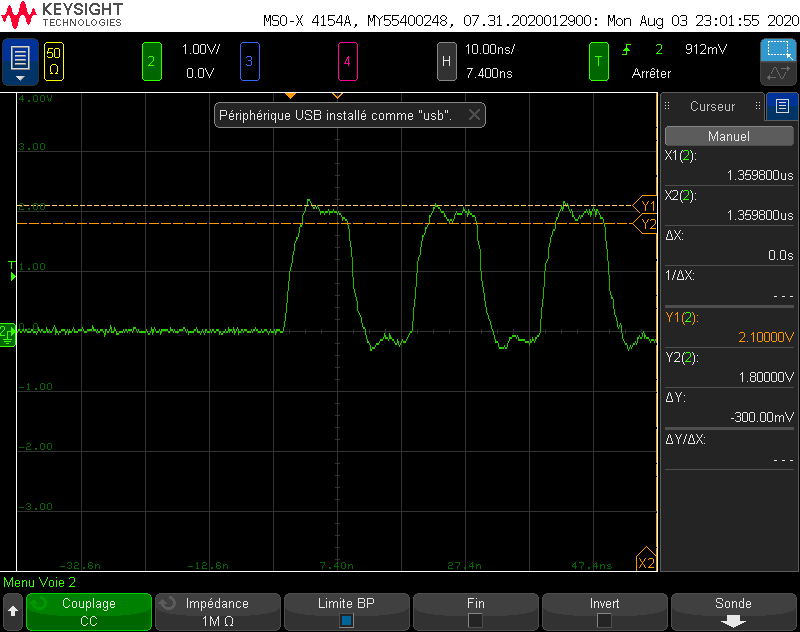

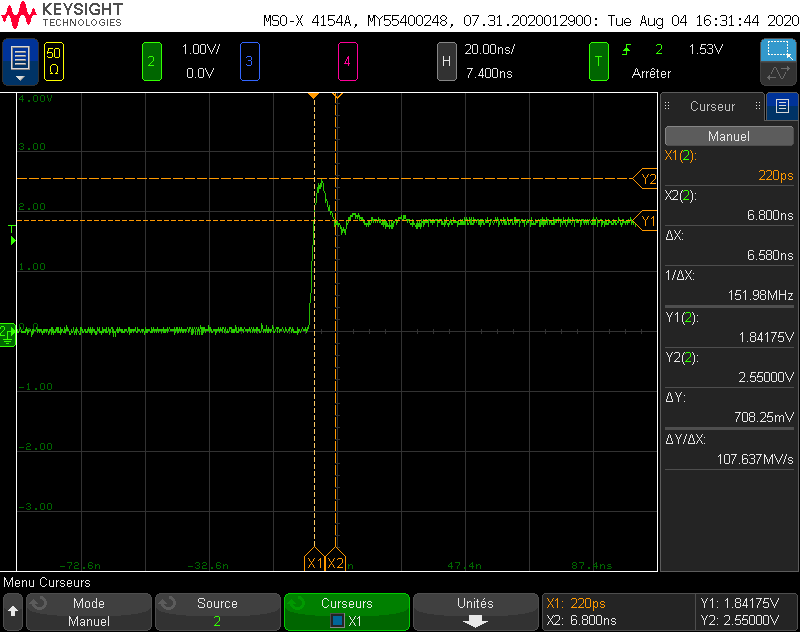

Checking the signal integrity on SDIO (WiFi HCI) & UART (BT HCI) inputs of WL1381MOD, we found some over/undershoots of 0.5~0.6V above 1.8V = Vio. WIth 33R series res they are limited to 0.3V.

The datasheet is rather strict:

- absolute max values: VDD_IO for CLK_IN (SDIO clock) and VDD_IO+0.5V for other pins.

- recommended values: max Vih = VDD_IO

If we increase further the series res, we are afraid of degrading the rise time and get a not-steep-enough clock or data rise...

Question : is this 0.3V over/undershoot acceptable considering it is only a transient violation of the spec ? Could this really impact long term reliability of the WL1831 ?

Thanks a lot for your support

Thomas