Hi All,

I have noticed SPI clock goes wrong when goes wrong at 16 Mhz, the problem exist in 8Mhz but it not noticeable.

Also updated CC3200 LauchPad XL to latest firmware 0.5.2.0.1

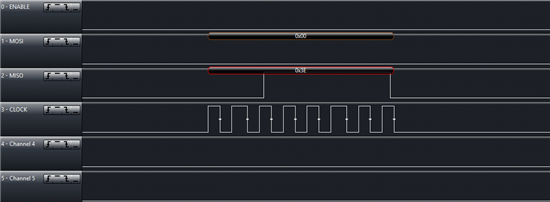

This is SPI at 8Mhz. As you see all clock cycle are not equal and frequency change between 7.14 Mhz to 8.33 Mhz

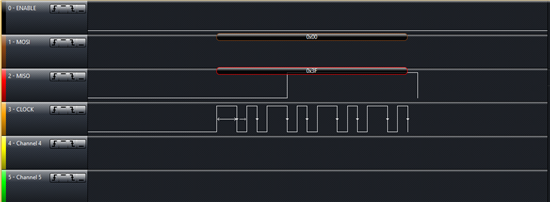

At 16 Mhz it get worse frequency goes from 16.67 Mhz to 25 Mhz

This is when we have hardware control

--------

MAP_SPIConfigSetExpClk(SSIBASE,MAP_PRCMPeripheralClockGet(PRCM_GSPI),

MAX_BITRATE/divider, SPI_MODE_MASTER, SSIMode,

(SPI_HW_CTRL_CS | SPI_3PIN_MODE |SPI_TURBO_OFF |SPI_CS_ACTIVELOW |SPI_WL_8));

MAP_SPIEnable(SSIBASE);

------

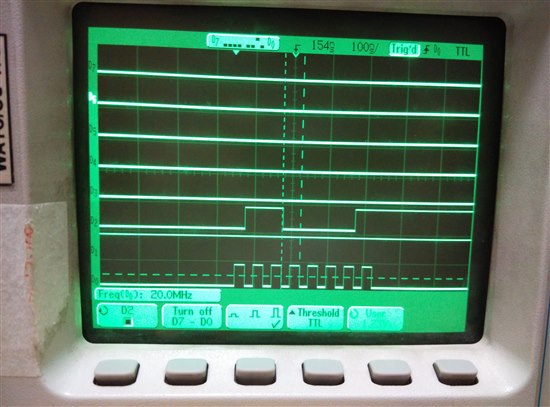

In case of software control, clock doesn't over 8Mhz and in all measurement sampling rate for Saleae is 50Mhz

Thanks,

Ali