Other Parts Discussed in Thread: LPSTK-CC1352R

A customer is using CC2652P7 as I2C master with 2 slave devices, and a few questions has been observed when using the I2C example from CC2652's SDK:

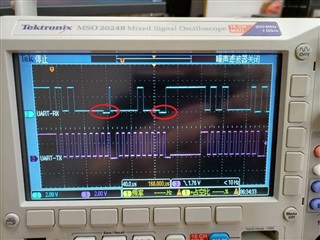

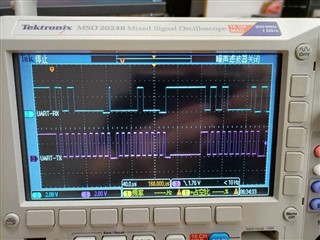

1. SCL was pulled low for a period of time with no good reason, as showed in the purple waveform in below picture. The same slave devices have been tested with other MCUs and no such case was found. Is there a way to tell whether the master or the slaves caused this?

2. A short pulse was found at the 9th SCL clock, see the blue waveform. What could be the cause and how to avoid it?

3. There were small "steps" in the SDA waveform, which appears to be drived by the slave, is it expected behavior?

The customer is using 2.2k ohm external pullup resistors for SDA and SCL pins, and a 33 ohm serial resistor on the SDA/SCL line. Does the resistors have something to do with the issues and what is the recommended values?

Thanks.

Best regards,

Shuyang