Tool/software: TI-RTOS

Hi All,

I am using CC2640R2F as SPI slave mode and have some issue. There are two cases of my test, case 1 success and case 2 not. Using the same code in both cases, and provided my code as follow. Please give me some hint. If Case 2 is necessary, can I use SPI slave mode?

Code:

uint8_t tbuf[5]={0x31,0x32,0x33,0x34,0x35},rbuf[5]; // Receive and transmit buffer

// Callback function

static void transferCallback(SPI_Handle handle, SPI_Transaction *transaction)

{

// Start another transfer

SPI_transfer(handle, transaction);

}

static void SimpleBLEPeripheral_taskFxn(UArg a0, UArg a1)

{

// Initialize application

SimpleBLEPeripheral_init();

// for SPI

// Callback function

SPI_init();

// Init SPI and specify non-default parameters

SPI_Params_init(&spi_params);

spi_params.bitRate = 4000000;

spi_params.frameFormat = SPI_POL0_PHA0;

spi_params.mode = SPI_SLAVE;

spi_params.transferMode = SPI_MODE_CALLBACK;

spi_params.transferCallbackFxn = transferCallback;

// Configure the transaction

transaction.count = 5;

transaction.txBuf = tbuf;

transaction.rxBuf = rbuf;

// Open the SPI and initiate the first transfer

spi_handle = SPI_open(Board_SPI0, &spi_params);

SPI_transfer(spi_handle, &transaction);

// Wait forever

while(true);

}

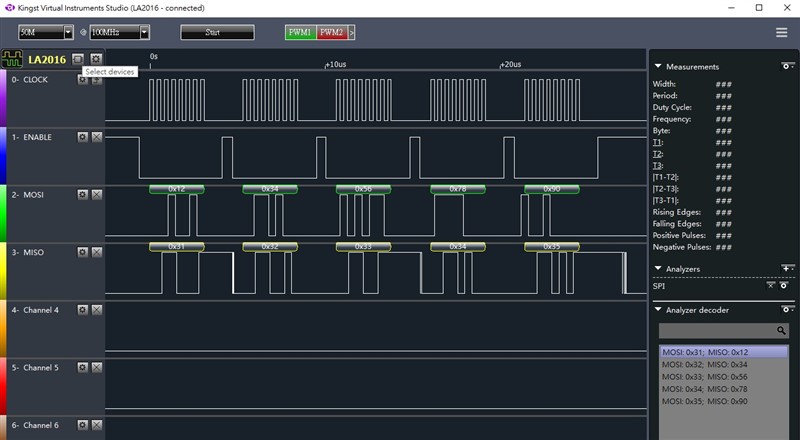

case 1:

The SPI master sends 5 bytes, the chip select (CS) pin goes low, a byte is transferred and then goes high. (fig 1)

=>CC2640R2F receive 5 bytes successfully.

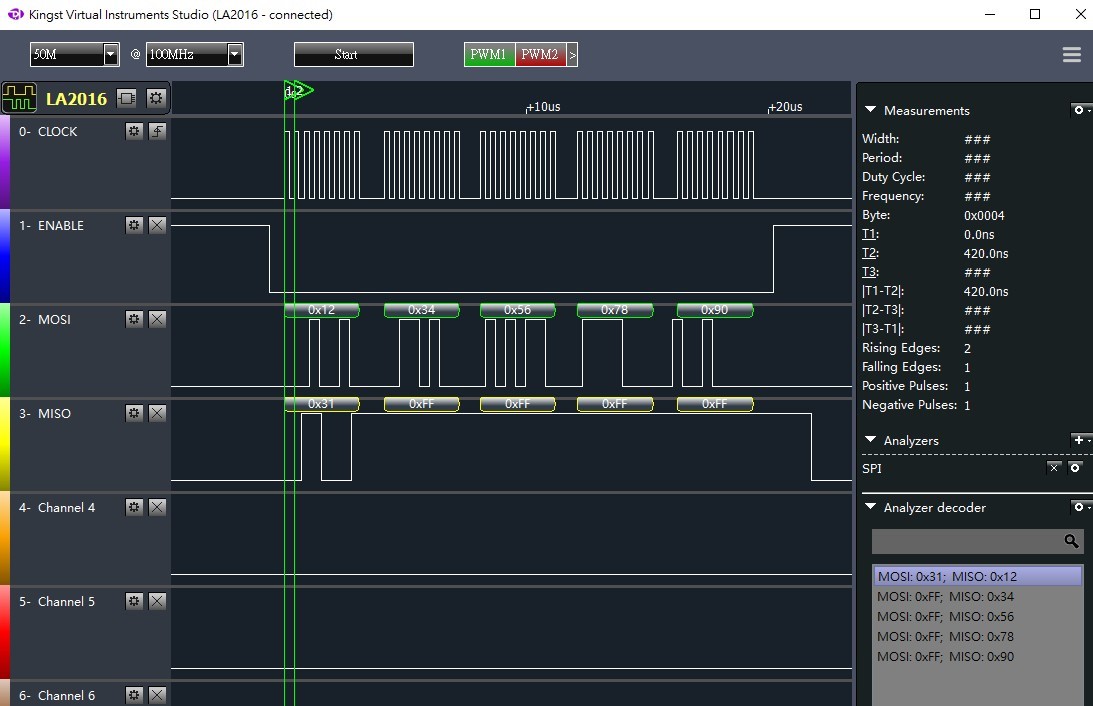

case 2:

SPI Master Sends 5 Bytes, Chip Select (CS) Pin holds Low during data transfer, goes High after 5-bytes transfer completes.(fig2)

=> not work, CC2640R2F only receive first byte successfully.

BR,

Jack