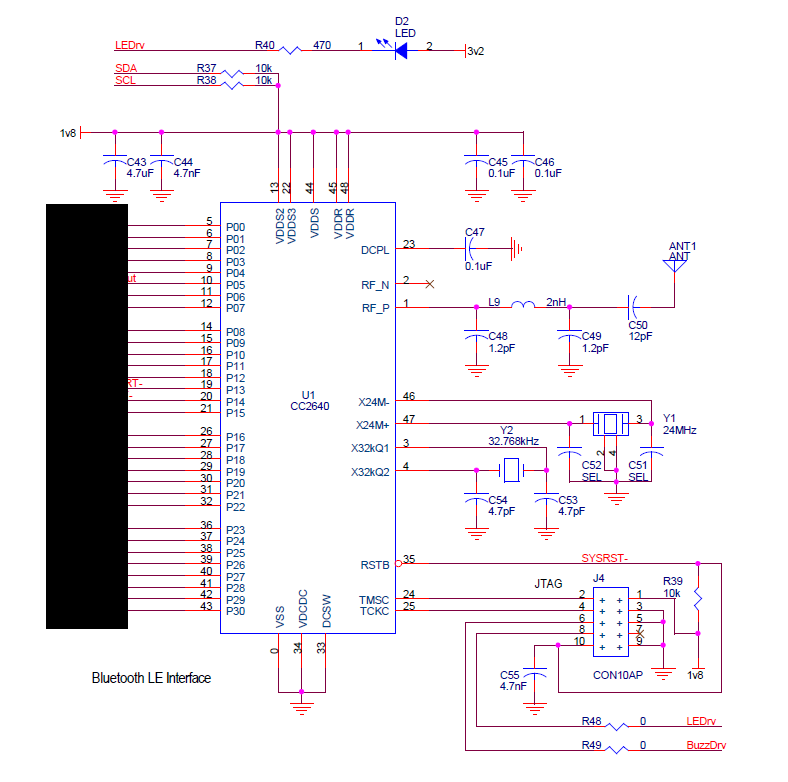

I have a CC2640 and am using a 32.768kHz crystal with 15pf load cap. The crystal shows 32.768kHz on the scope but the output from the CC2640 GPIO is 31.25kHz on the scope. DDI0_OSC.CTL0.SCLK_LF_SCR_SEL = 0x3 (XOSC_LF) and DDI0_OSC.STAT0.SCLK_LF_SRC == 0x0 (XOSC_LF), so the crystal apparently is not being used. However, BLE advertising, connection and notification seem to be working well. I understand the load cap is out of spec. I will try 6-12pF. But will that solve my problem? I need to get 32.768kHz out from the CC2640 in order to drive another IC.

Thanks!