Other Parts Discussed in Thread: , DLP-7970ABP

Hi,

we recently found a problem in Read Single Block we never seen before.

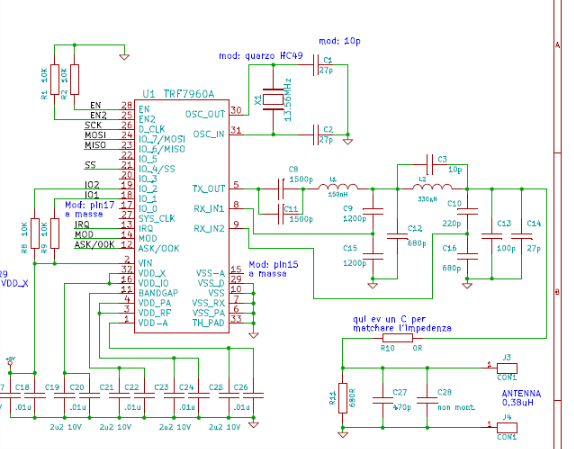

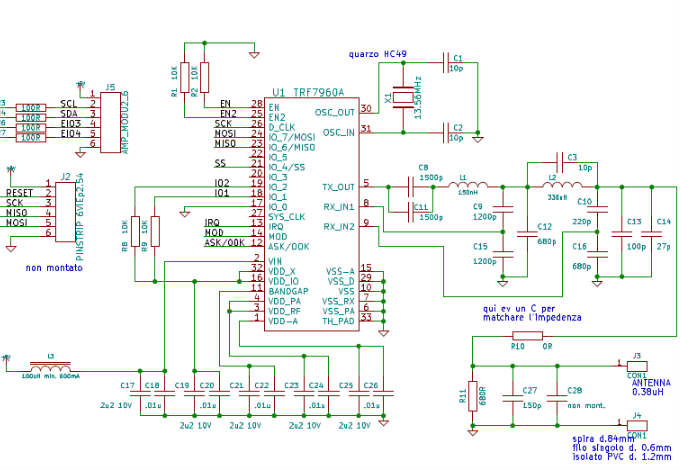

It seems it happens after we slightly modify our RFID board simply integrating a impedance in the board circuit instead of connect it externally.

The problem is that in rare cases the Read Single Block command returns a wrong value in the last byte of the block.

The wrong value is always the same if the data in the block remains the same but it changes if data change.

The datalogger shows that everything is correct in the SPI data exchange, it is always the same (same data, same timing) when the value is correct or incorrect and it is compatible with TI examples.

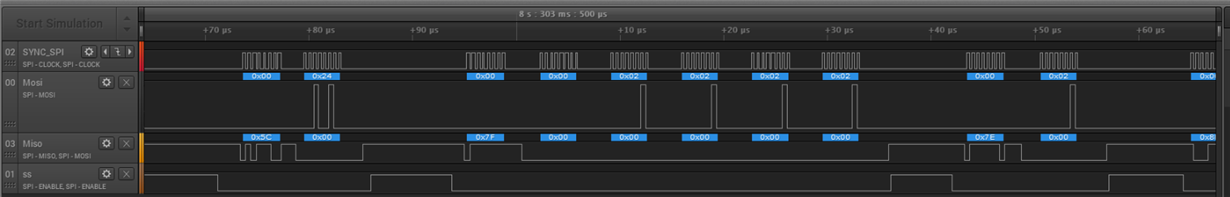

This is the correct sequence that happens almost every time (all bytes of the block are correctly 0x02):

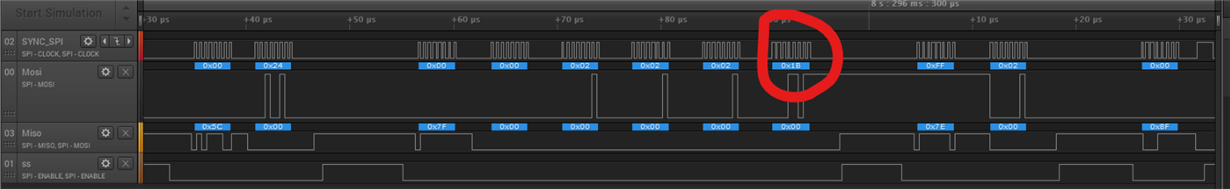

This is the wrong sequence (all values and timings are the same, even the ones not shown in the picture) but the last byte is not 0x02 but 0x1B

Anyone have an idea of the cause of problem?

Our dubt is: do we need to implement the workaround 4 described in SLOA155 "Wrong Data Due to Overshoots"?

It refers to ISO14443A decoder but we use ISO15693. If so can you explain better how to implement it?

We thing we are using a TRF7960 instead of TRF7960A (we are checking with the designer of our board). How can we distinguish them? Could we try to update the chip to TRF7960A?

Thank you in advance.

Best regards

Alessandro