Other Parts Discussed in Thread: WL1831

Hello team,

When you get a chance please see below customer question:

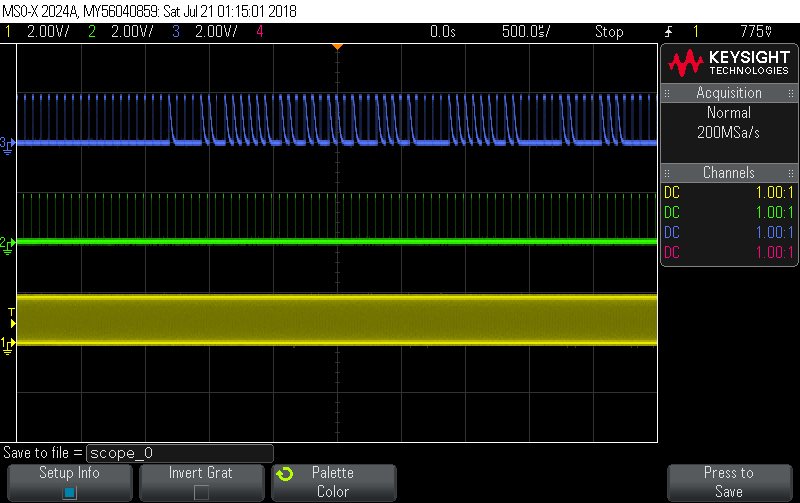

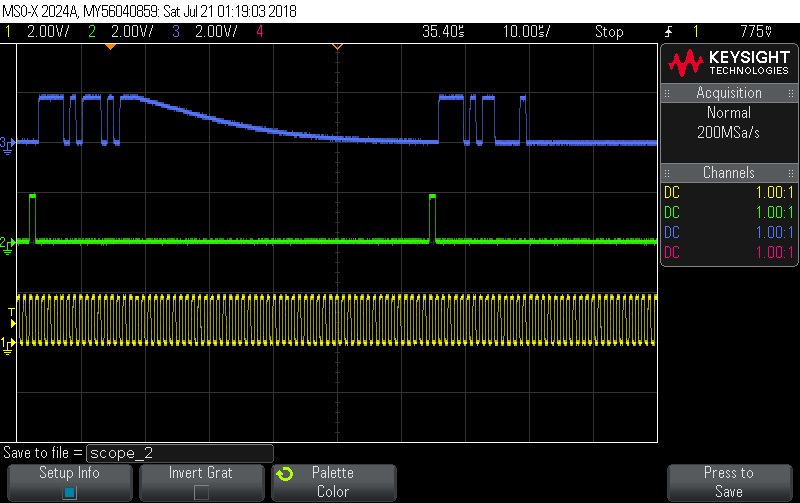

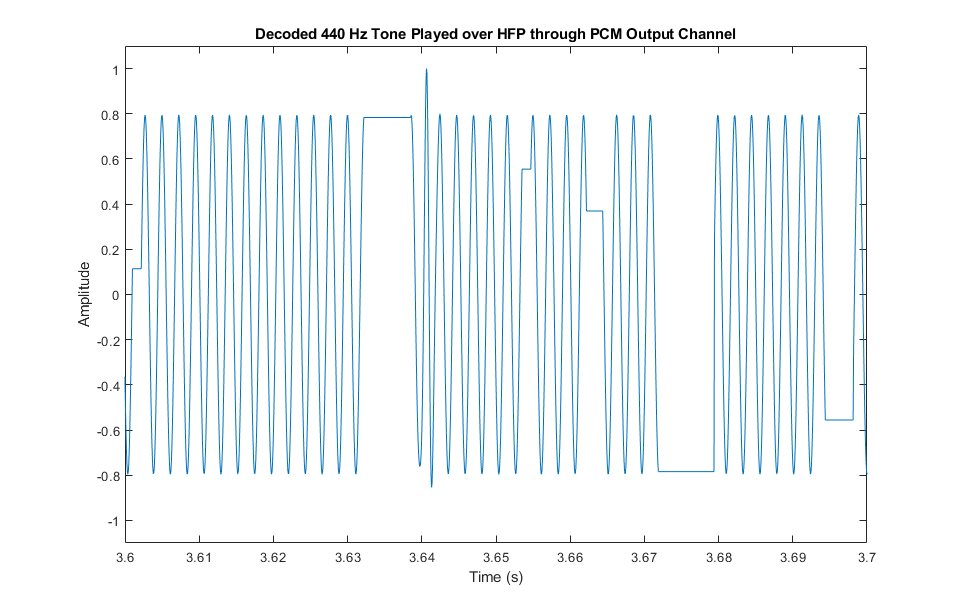

I am working to resolve a poor audio quality issue we are experiencing in our application. I believe I have tracked down the issue to being a sampling rate mismatch between the WL1831MOD wifi/bt transceiver and our WM8281 audio codec.

I have been reviewing the data sheet available for the WL1831MOD and have discovered that the audio bus (AUD_CLK, AUD_IN, AUD_OUT, FSYNC) being used for transferring audio data to/from the codec can be used in either slave or master mode. Currently is looks to be in master mode with an output sampling rate that is different than what can be selected in the audio codec. Do you have any more reference information on how the master or slave mode is selected and configured? If it's easier to discuss over the phone, please call me