Hi, I've been running into an issue with the ADS131M06 where if I try to decrease Oversampling Rate to anything below 4096, I get data from the previous sample bleeding into the next sample for each channel. This has effectively limited the overall sampling rate and can only be improved by increasing fCLKIN. I have tried with clock-rates of 2MHz and 4MHz but the same 4096 OSR limit has remained, and would assume it to stay if we went up to 8MHz.

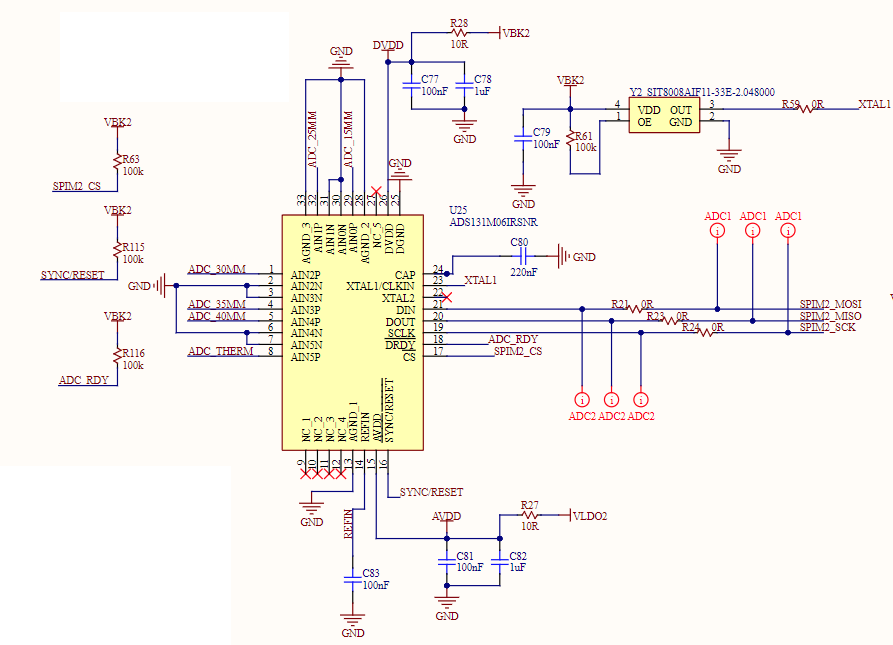

Hardware wise, we believe we have stuck to the layout example in the datasheet, and have probed the input to each channel without observing any such bleed in the input signal.

For our application each sample is from a completely different source, and there cant be any bleed from previous samples. Is this expected behavior? is there a setting I'm missing to prevent this from happening, or a hardware configuration change?

Thanks,

- Brett