Hello team:

Currently we have a product solution that use 1 941 to connect 2 948, to drive 2 screens and each one has touch.

According to https://www.ti.com/lit/an/snla308a/snla308a.pdf, Figure 10-4. INTB Logic in Splitter Interrupt Mode

we need reading the isr(0xC7) to clearded to high;

In fact, we didn't do anything,but the interrupt automatically increases, and the interrupt logic is consistent with port0;

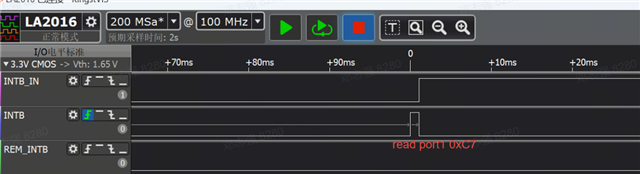

The following are the actual measurement results of the logic analyzer

For the 941 in splitter mode:

we Set SER register 0x30=0x01; and 0xC6=0x01;

In fact, with this setup, two independent TP can already work properly;

but, we Set SER register 0x30=0x01; and 0xC6=0x21;

then,touch the screen , the port1 intb pin we got nothing; as shown in the following figure

Is there any mistake in our understanding of the document? The behavior of the interrupt was not consistent with the manual documentation, so we were confused?

could you please support this issue?