Other Parts Discussed in Thread: ALP

Tool/software:

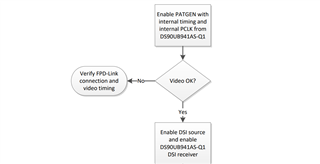

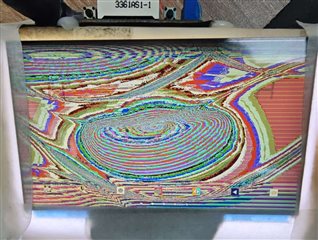

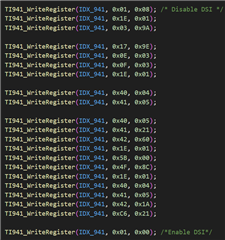

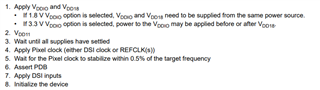

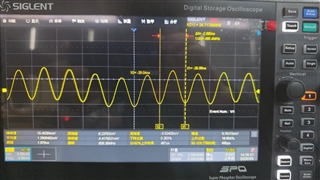

The DS90UB941 configuration register combined with the DS90UB948 outputs 1920*1080 images,

But refer to the programming example of zhcaag5a.pdf manual to modify, the specific register is written as follows, but it can not be displayed on the screen, and read 0x06 register through 941 address can not read the address of the unstring 948, directly read with 948 address, The returned status value is STATUS_I2C_RECEIVED_NACK, there is no idea, please guide to deal with it, thank you