Other Parts Discussed in Thread: SN74LVC1G08

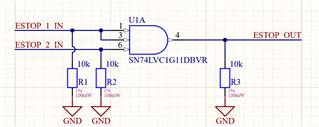

I am looking for a design where I can connect 2 safety signals to 1 safety input on a MCU.

Voltage levels are 3V3. When either one of the safety signals drops to 0V/floating, the MCU input should do the same.

A logical step would be to use an AND gate, for example, the SN74LVC1G11. Being a safety system, we need to analyze the weaknesses in the system.

In order to implement this AND gate, we need to be sure that all failure modes of the Gate are considered safe. In other words, the output cannot be stuck at VCC when either input is low.

This particular AND gate shows great MTBF values, but I do not see a Failure Mode Distrubution (FMD) report. I did find one for the SN74LVC1G08, which does not look very promising for my application.

I am wondering if it is possible to find an AND gate without failure modes that could short the output to VCC.