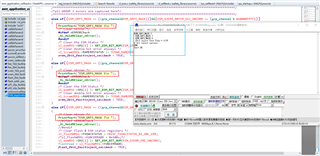

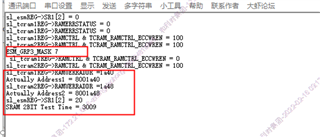

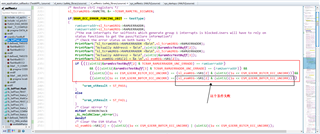

hi,When testing SRAM 2bit ECC fault injection, under normal circumstances, the interruption of ESM3.3 and ESM3.5 should be triggered. However, according to the debugging and printing information, the FLASH of ESM3.7 also caused an uncorrectable error, but I did not cause the FLASH fault. What is the reason for this? Is it normal? thanks a lot.