- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I am using the ti-cgt-arm_20.2.0.LTS compiler.

I am trying to allocated an interrupt routine to a 4byte alligned address.

For this, I'm doing the following:

.c file:

__attribute__ ((aligned (4), section (".my_DMTimer_Isr_section"))) void DMTimer2_Isr(void)

{

...

}

.h file:

__attribute__ ((aligned (4), section (".my_DMTimer_Isr_section"))) void DMTimer2_Isr(void);

.ld file:

.my_DMTimer_Isr_section: ALIGN(4)

{

*(.my_DMTimer_Isr_section)

} > DMEM0

where:

DMEM0 : ORIGIN = 0x00070000 , LENGTH = 0x0000FFE0 /* 64 KiB */

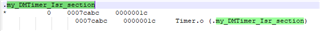

The result in the map file is the following:

It looks the section my_DMTimer_Isr_section is 4 byte aligned, but the function starts at +1 byte.

What would be the reason for this missalignement?

Thank you and have a nice day!

Mihai Mihaila.

It looks the section my_DMTimer_Isr_section is 4 byte aligned, but the function starts at +1 byte.

What processor is used and is the code compiled for ARM or THUMB mode?

Branch and Call Sequences Explained explains that:

Address-based interworking uses the lowest bit of the address to determine the instruction set at the target. If the lowest bit is 1, the branch will switch to Thumb state. If the lowest bit is 0, the branch will switch to Arm state. Note that the lowest bit is never actually used as part of the address as all instructions are either 4-byte aligned (as in Arm) or 2-byte aligned (as in Thumb).

Hello,

I am using a Cortex-M3 and the code is compiled for THUMB Mode.

Thank you,

Mihai M.

Hi Mihai,

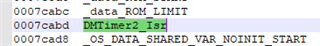

Sorry for the delayed response over the Easter break. I agree with Chester's answer. The function is placed in the section at 0x7cabc. But the last bit being set signifies that it is a THUMB instruction.

To verify this, you can look at the disassembly view in CCS. Start a debug session with the project and check the disassembly window and take a look at the address 0x7cabc. It should be the DMTimer2_Isr function that is placed there.

PS: Thank you for the answer Chester.

Regards,

Sid

Thank you very much for the answers!

I was able to confirm in disassembly that the actual address of DMTimer2_Isr is 0x7cabc.

Have a great day!