Tool/software:

Hi,

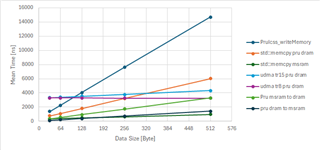

i need to transfere data from the msram to pru dram or pru shared dram and back. The background is that i programmed the pru0 to act as a rgmii driver to transmit and receive at 1Gbps. I need to transmitt around 300Bytes which takes around 3us only for the rgmii. I took a few measurements to determine which way to get the data from pru dram to msram and vise versa.

The PruIcss_writeMemory is, depending on the data amount, slowest and cant by used for my purpose.

Using memcpy to copy data directly from r5f memory to pru dram is with 4us for ~300Byte also to slow.

I used the udma_memcpy_interrupt example and modified it for the two measurments. Both seem really slow for an dma. Maybe that can be improved?

The fasted way i found is letting the pru handle the copy. For that i use lbbo msram ->sbco dram and lbco dram -> sbbo msram.

Another time consuming factor are the interrupts between pru and r5f. r5f to pru interrupt takes around 200ns, Pru to r5f around 890ns.

The next graph shows the data transfere time from copying the data from r5f to msram -> send interrupt to pru -> pru copy data from msram to dram. And the other way around:

Combining that with the 3us for rgmii results in around 6.5us for reading data and 5.5us for writing. I need this times closer to 4us each. Is there a way to get the data faster from msram to pru dram?

Thanks and Regards

Lucas