Part Number: TMS320F28388D

Other Parts Discussed in Thread: C2000WARE

I adapted the fsi_ex8_ext_p2pconnetion_Xx projects to work on our custom board containing two TMS320F28388D's. I want to use the FSI for inter-chip coms. From the tx chip, I send a known fixed pattern (0x1,0x2,0x3,0x4,0x5,0x6) and not the increasing pattern used by default.

On the receiving side I have the following rx_isr:

uint16_t rxDataArray[16];

__interrupt void fsiRxInt1ISR(void)

{

rxEventSts = FSI_getRxEventStatus(FSIRXA_BASE);

fsiRxInt1Received = 1U;

//

// Increment number of data frames received

//

if((rxEventSts & FSI_RX_EVT_DATA_FRAME) != 0)

{

dataFrameCntr++;

FSI_readRxBuffer(FSIRXA_BASE, rxDataArray, nWords, 0);

FSI_setRxBufferPtr(FSIRXA_BASE, 0U);

}

//

// Clear the interrupt flag and issue ACK

//

FSI_clearRxEvents(FSIRXA_BASE,rxEventSts);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP4);

}

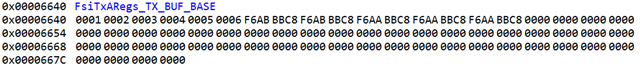

But looking at the array it always has an offset

If I understand correctly the rxbuffer should be a circular buffer and because I set the nword length to 6 it should loop the circ buf every 6 words, correct? And because I call the FSI_setRxBufferPtr function and set it to 0, it should always receive the first byte to position 0 correct? What am I missing?

Kind regards

EDIT:

I don't think that the clock settings should affect the FSI in a manner that would cause this issue, but I also changed device.h to use new cristal

//

// 18.432MHz XTAL on controlCARD. For use with SysCtl_getClock() and

// SysCtl_getAuxClock().

//

#define DEVICE_OSCSRC_FREQ 18432000U

//

// Define to pass to SysCtl_setClock(). Will configure the clock as follows:

// PLLSYSCLK = 18.432MHz (XTAL_OSC) * 54 (IMULT) / (1 (REFDIV) * 5 (ODIV) * 1(SYSDIV))

//

#define DEVICE_SETCLOCK_CFG (SYSCTL_OSCSRC_XTAL | SYSCTL_IMULT(54) | \

SYSCTL_REFDIV(1) | SYSCTL_ODIV(5) | \

SYSCTL_SYSDIV(1) | SYSCTL_PLL_ENABLE | \

SYSCTL_DCC_BASE_1)

//

// 200MHz SYSCLK frequency based on the above DEVICE_SETCLOCK_CFG. Update the

// code below if a different clock configuration is used!

//

#define DEVICE_SYSCLK_FREQ ((DEVICE_OSCSRC_FREQ * 54) / (1 * 5 * 1))

//

// 50MHz LSPCLK frequency based on the above DEVICE_SYSCLK_FREQ and a default

// low speed peripheral clock divider of 4. Update the code below if a

// different LSPCLK divider is used!

//

#define DEVICE_LSPCLK_FREQ (DEVICE_SYSCLK_FREQ / 2)

//

// Define to pass to SysCtl_setAuxClock(). Will configure the clock as follows:

// AUXPLLCLK = 20MHz (XTAL_OSC) * 50 (IMULT) / (2 (REFDIV) * 4 (ODIV) * 1(AUXPLLDIV) )

//

#define DEVICE_AUXSETCLOCK_CFG (SYSCTL_AUXPLL_OSCSRC_XTAL | SYSCTL_AUXPLL_IMULT(50) | \

SYSCTL_REFDIV(2U) | SYSCTL_ODIV(4U) | \

SYSCTL_AUXPLL_DIV_1 | SYSCTL_AUXPLL_ENABLE | \

SYSCTL_DCC_BASE_0)

//

// 125MHz AUXCLK frequency based on the above DEVICE_AUXSETCLOCK_CFG. Update

// the code below if a different clock configuration is used!

//

#define DEVICE_AUXCLK_FREQ ((DEVICE_OSCSRC_FREQ * 50) / (2 * 4 * 1))