Other Parts Discussed in Thread: SYSCONFIG

Hi Expert,

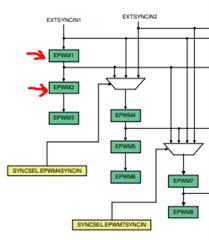

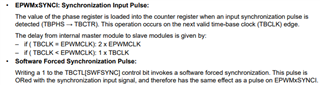

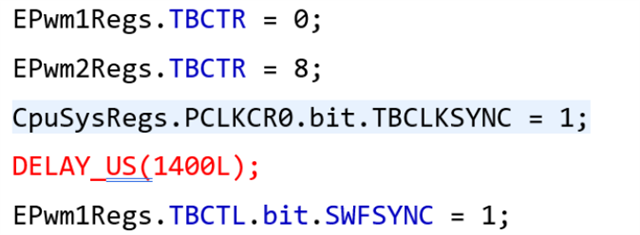

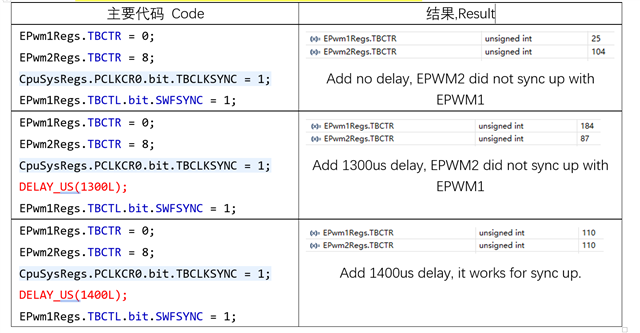

My customer use several PWM module that require sync event, they use software to sync EPWM1, they find that after set TBCLKSYNC to 1, they have to use Delay function which delay 1400us so that EPWM2 will sync up with EPWM1, otherwise there will fail to sync up.

The PWM period is only 4us, Could you help explain why require delay so long that it can work normally? thanks.