Hello,

This is maybe a question for a TI engineer, or anybody else with a detailed knowledge of the MSP430F5438A's I2C port.

We're using the MSP430F5438A connected to a ZSC31014 bridge amplifier chip using the I2C bus in master mode, from the MSP's port UCB3. Our I2C bus uses 4k7 pullups.

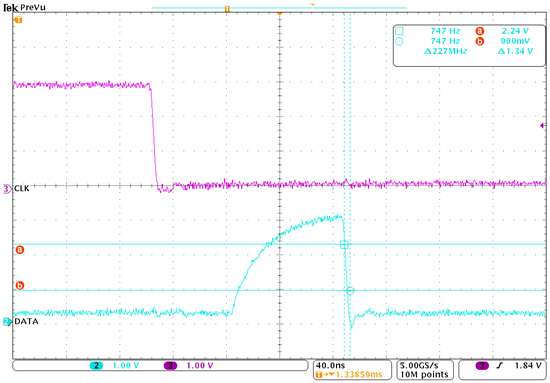

We've been having a problem that the MSP4305438A's I2C port produces a glitch spike on the SDA line, between what we perceive to be the end of each start bit and the beginning of the MSbit 6 of the address byte, as follows:

Zooming in on the glitch pulse:

We fully understand that this glitch spike should not matter to I2C operation. However, unfortunately the ZSC31014 datasheet (on page 24) states that its I2C port departs from the normal I2C specification: "A falling SDA edge is not allowed between the start condition and the first rising SCL edge. If using an I2C address with the first bit 0, SDA must be held low from the start condition through the first bit."

This combination of the MSP430 I2C glitch pulses, and the ZSC31014's susceptibility to them, resulted in us having reliability problems with this chip. Our workaround is to configure the ZSC chip to have an address with its bit 6 set (e.g. we’re now using 0x42) - this turns the glitch pulse into a nice clean "high" bit for the address bit 6 duration, which gets rid of the problematic falling edge.

However, we would like to know if there is any way of stopping the MSP430F5348A's I2C port from generating this glitch pulse in the first place, for I2C addresses below 0x40? For example, any "trick" settings of the MSP430's I2C register settings? Or, are these glitch pulses an unavoidable by-product of the normal MSP430 I2C port operation?

Many thanks in advance,

Bart

(P.S. I've already seen the separate "msp430 I2C glitch / spike issue" forum entry at http://e2e.ti.com/support/microcontrollers/msp430/f/166/t/237128.aspx)