Hello,

We are currently using an UCC21750 driver on an application (Three phase inverter 400V 10kW).

On some condition (under analysis), the driver stop the PWM during approximately 1ms.

this behavior seems to resemble to a activation of the internal under voltage look up or activation of the short circuit protection.

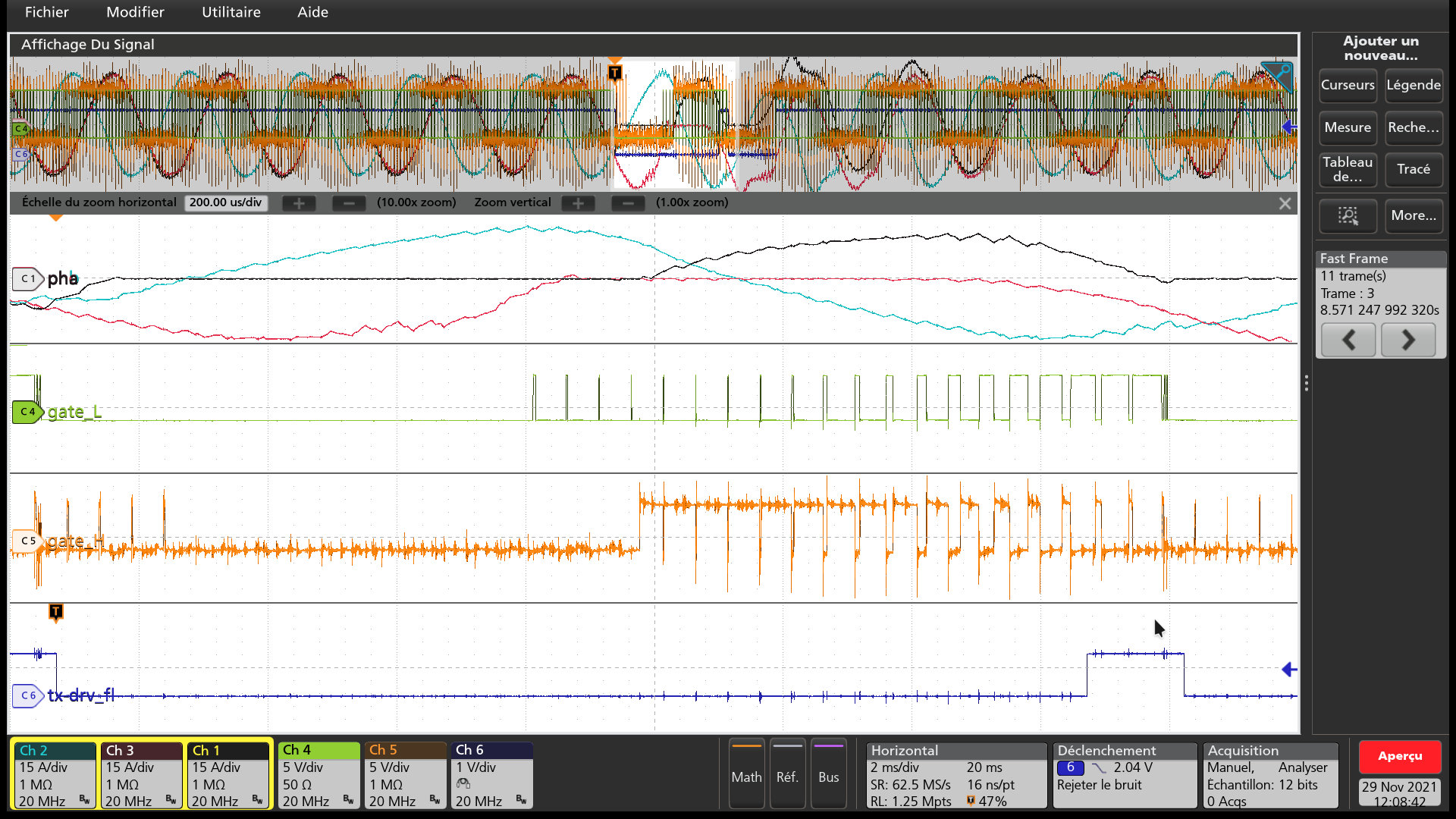

C4 : Gate voltage with high rejection differential probe

C5 : Gate voltage with differential probe

C6 : DRV flag from all drivers with addition monitoring

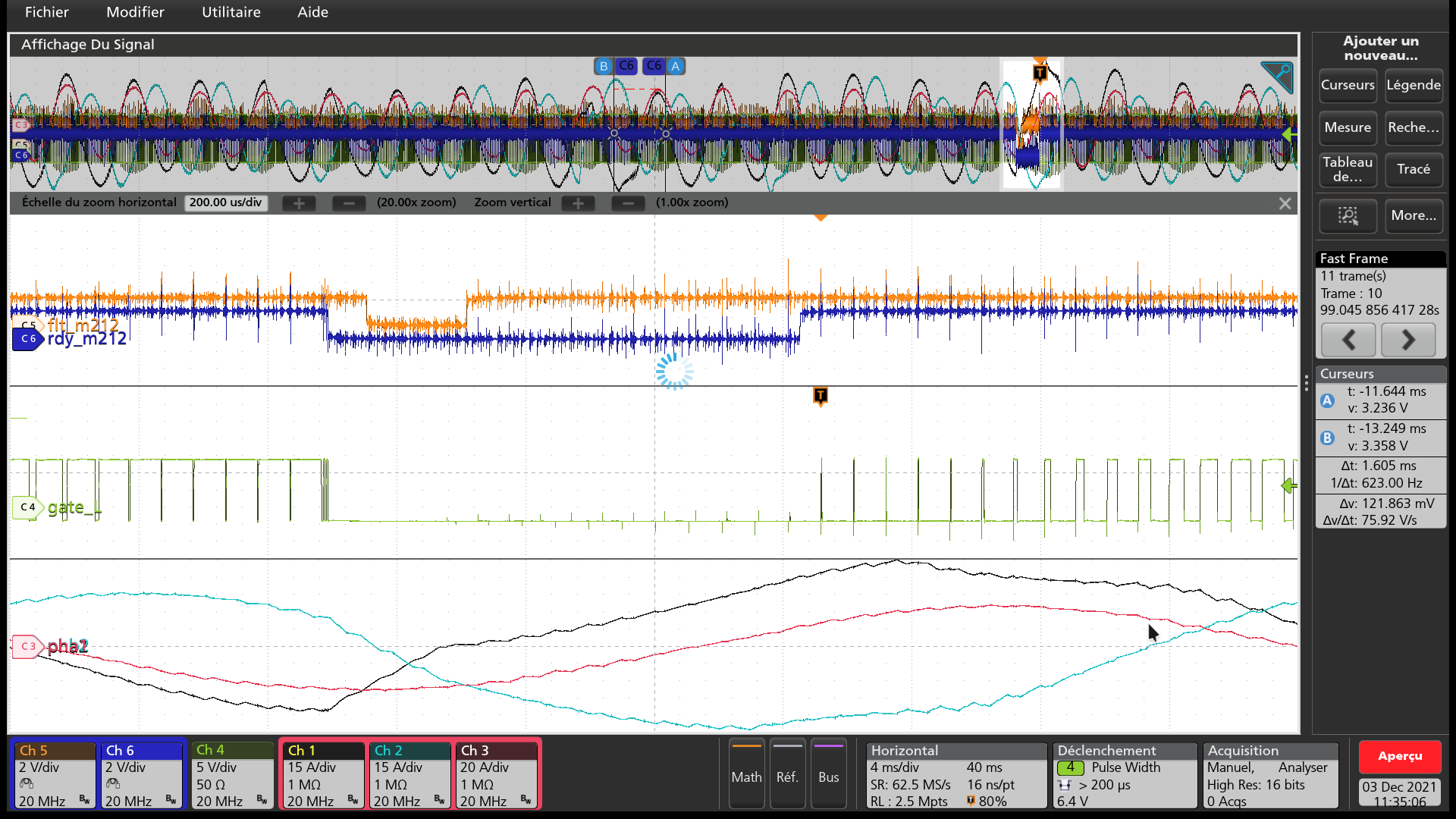

C4 : Gate voltage with high rejection differential probe

C5 : FLT FLAG of UCC21750

C6 : RDY FLAG of UCC21750

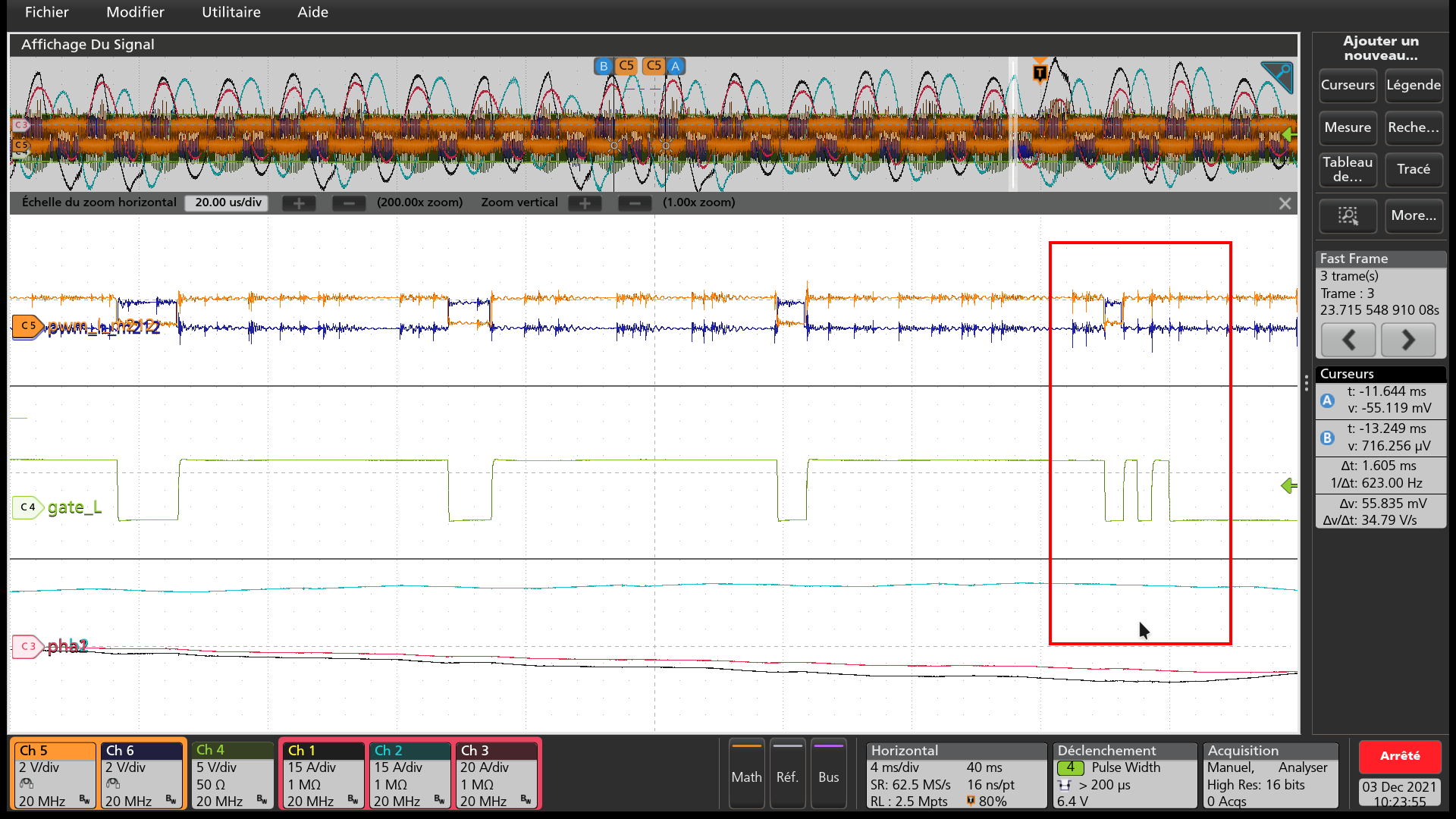

When the driver stop, we observe an additional pulse on the gate voltage before the ‘long stop’ of the driver (tFLTMUTE or tRDYHLD).

Do you have any idea what can cause this behavior?

C5 and C6 : PMW_H and PMW_L input of driver

C4 : Gate voltage with high rejection differential probe

Other problem, the RDY flag is raised with VCC=3,3V and VDD=15V

Do you have any idea what can cause this behavior?

Many thank for your support.