Other Parts Discussed in Thread: TPS65218D0

Hi,.

A customer of ours is building a custom board using the AM4378.

In the board they are currently building, the power is supplied from the PMIC (TPS65218D0) to the CPU (AM4378).

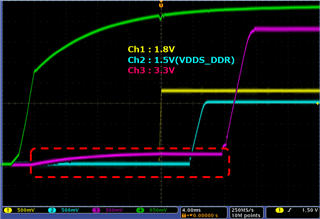

AM4378 does not use RTC, and IO voltage is used under the condition of 2 voltages (3.3V and 1.8V), so it should be activated in the order of 1.8V → VDDS_DDR(1.5V) → 3.3V as shown below from the power-up sequence (Figure 5-7.) described in the data sheet.

After checking the waveforms of the board they created, as shown in the figure below, the order in which the specified voltage of each power supply is reached is as required: 1.8V → VDDS_DDR(1.5V) → 3.3V, but in the area enclosed by the red dashed line, the voltage is reached via IO (I2C interface) with another board → PU resistor for I2C (1k The red dashed line indicates that the voltage is increased by about 0.25V for a period of 24ms due to the power supply sequence to the AM437x.

Please confirm if there is a problem with the power supply sequence to AM437x.

Best Regards,

Kouji Nishigata