Part Number: TDA4VM

Other Parts Discussed in Thread: AB15

Tool/software:

Hello TI experts,

We output a 2560*800 SuperFrame through TDA4 DSI, which is then split into two 1280*800 by DS981;

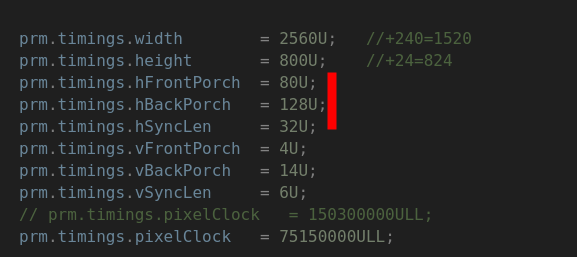

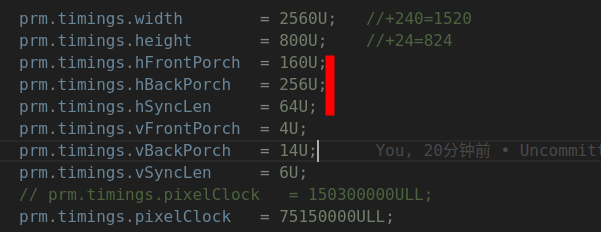

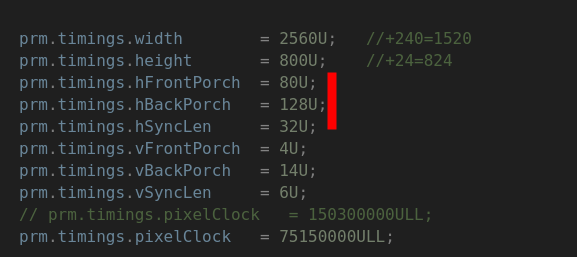

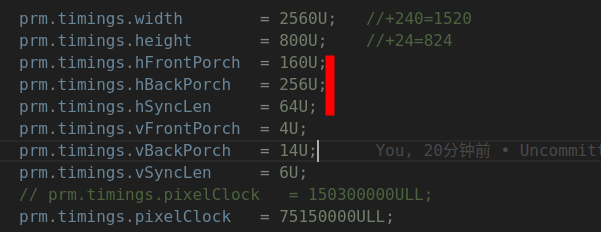

The LCD timing is:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TDA4VM

Other Parts Discussed in Thread: AB15

Tool/software:

Hello TI experts,

We output a 2560*800 SuperFrame through TDA4 DSI, which is then split into two 1280*800 by DS981;

The LCD timing is:

Hi Barry,

I see this is a duplicate of this thread: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1447388/tda4vm-h-timing-superframe/5555659?tisearch=e2e-sitesearch&keymatch=%2520user%253A585052#5555659

#1: In TDA4, does the H direction blanking area of SuperFrame timing have to be multiplied by 2?

No, if it is a single frame, then blanking intervals should not need to be multiplied by 2.

That is, if reduced blanking mode is supported on the display. For example, below is an example from VESA-DMT-1.13.pdf which is a document that has some predefined display monitor timings. For reduced blanking, both 1280x800 and 2560x1600 use 48pixels for HFP, 32 for HSync, and 80 for HFB.

#2:If the H direction is not multiplied by *2, will this timing affect the effective output of DSI_TX?

If you are saying if H direction "blanking period" is not multiplied by *2, whether it affects throughput of data out, then no it will not affect throughput, but it will instead affect whether there are video artifacts or not. Monitors take a certain range of blanking period, and if the programmed period is out of the tolerable range, then video artifacts may appear.

If instead you are asking if H direction "resolution" is not multiplied by *2, whether it affects throughput of data out, then yes, it will affect throughput since less data is being sent.

Regards,

Takuma

Hi Takuma,

As long as 1280*800 is a single frame.

As long as 2560*800 is a SuperFrame.

The problem now is:

The serializer TI ds981 used does not support splitter mode, so we have to use crop mode to split.

In this case:

#1: How should the timing be set in TDA4? When superframe, blank blanking should be multiplied by 2?

#2: How much should the startx and endx, starty and endy of crop in ds981 be set?

Looking forward to your reply.

Hi Barry,

To learn about timing parameters, I would recommend using the EVM and connecting to a DP monitor. Then you may use kmsprint to print out the CRTC. For example:

root@j784s4-evm:~# kmsprint

Connector 0 (40) DP-1 (connected)

Encoder 0 (39) NONE

Crtc 0 (38) 3840x2160@30.00 297.000 3840/176/88/296/+ 2160/8/10/72/+ 30 (30.00) 0x100005 0x40

Plane 0 (31) fb-id: 67 (crtcs: 0 1) 0,0 3840x2160 -> 0,0 3840x2160 (AR12 AB12 RA12 RG16 BG16 AR15 AB15 AR24 AB24 RA24 BA24 RG24 BG24 AR30 AB30 XR12 XB12 RX12 XR15 XB15 XR24 XB24 RX24 BX24 XR30 XB30 YUYV UYVY NV12)

FB 67 3840x2160

Connector 1 (50) eDP-1 (disconnected)

Encoder 1 (49) NONE

root@j784s4-evm:~#

You may cross check these numbers with VESA documentation, or (since your resolution is non-standard) calculate the timing parameters based on specification. Searching online, there should be calculators that you may reference. For example, below is output from one of the calculators you may find online:

As for startx, endx, starty and endy, this is specific to your application. I would assume you want just the corners of the area of active frame.

Regards,

Takuma