Tool/software:

Hi expert,

Our customer find serious image fragmentation issue on TDA4VE as the below video shown. Could you please help check how to debug?

SDK:

ti-processor-sdk-rtos-j721s2-evm-08_06_01_03

Camera:

4*1920*1536@25fps

Issue describtion:

1. 4 cameras connected to CSI-RX and TDA4VE output the video to cookpit thru ethernet. We can find serious image fragmentation in about 5 secs.

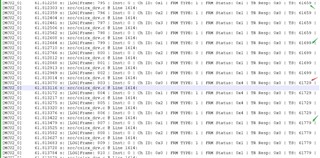

2. We find capture statistic, CRC/ECC/OVERFLOW keeps 0 in MCU2_0, but frame drop count keeps increasing;

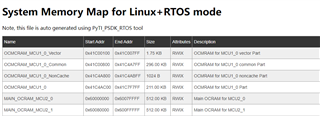

3. DDR statistic as below:

Test and Result:

1. If only 1 camera is connected, there is no issue;

2. We try to increase the buffer of capture node from 4 to 6; frame drop count almost disappear, and there is some improvement to this issue, but cannot totally fix it;

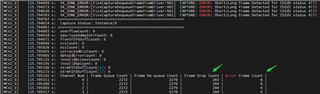

capture statistic as below:

3. If we disable BEV fastray and infopost in C7, there will be no issue;

4. We try to modify the CSIRX driver config as below, and reproduce probability is decreased from 5s/1time to 1minute/1time;

|

file |

function |

change |

|

pdk_j721s2_08_06_01_03/packages/ti/drv/csirx/csirx.h |

increase chCfgPrms->rxChParams.addrType = TISCI_MSG_VALUE_RM_UDMAP_CH_ATYPE_NON_COHERENT; chCfgPrms->rxChParams.busOrderId = 12U; |

5. We try to follow suggestions in below E2E link to modify CSIRX driver. But the error is reported.

|

file |

function |

change |

|

packages/ti/drv/csirx/csirx.h |

Csirx_chCfgInit |

add "chCfgPrms->rxChParams.addrType = TISCI_MSG_VALUE_RM_UDMAP_CH_ATYPE_NON_COHERENT;" line at the end of the function. Change below statement UdmaChRxPrms_init(&chCfgPrms->rxChParams, UDMA_CH_TYPE_RX); to UdmaChRxPrms_init(&chCfgPrms->rxChParams, UDMA_CH_TYPE_RX_UHC); |

|

packages/ti/drv/udma/src/udma_ch.c |

UdmaChUtcPrms_init |

change below statement utcPrms->addrType = TISCI_MSG_VALUE_RM_UDMAP_CH_ATYPE_PHYS; to utcPrms->addrType = TISCI_MSG_VALUE_RM_UDMAP_CH_ATYPE_NON_COHERENT; //TISCI_MSG_VALUE_RM_UDMAP_CH_ATYPE_PHYS; |

|

packages/ti/drv/csirx/src/csirx_drvUdma.c |

CsirxDrv_setChUdmaParams |

change below statement chType = UDMA_CH_TYPE_RX; to chType = UDMA_CH_TYPE_RX_UHC; |

After above modification, capture node report below error when MCU2_0 start up.

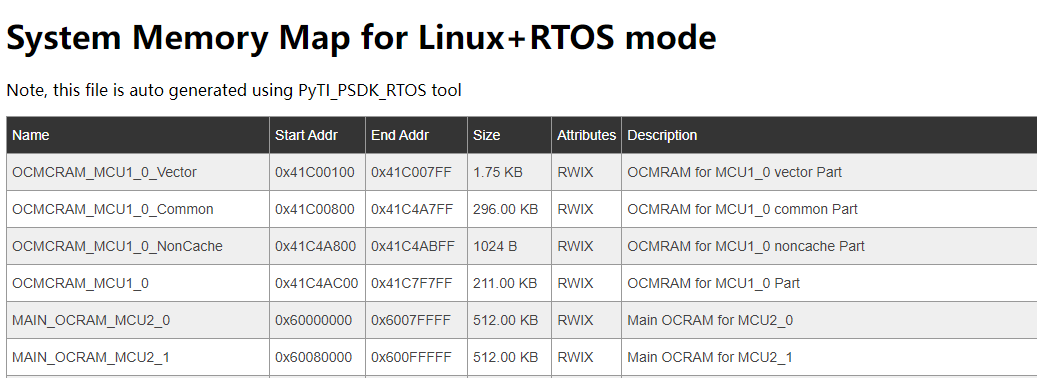

About the issue that UDMA_CH_TYPE_RX_HC and UDMA_CH_TYPE_RX_UHC channel allocation fail, customer look into Udma_rmAllocRxHcCh() and Udma_rmAllocRxUhcCh() and find that numRxHcCh and numRxUhcCh are 0.

Customer traced the code and found that it uses Udma_rmGetSciclientDefaultBoardCfgRmRange() to Query all the resource ranges from the Sciclient Default BoardCfg. if customer wants to use RX hc and uhc channel, what config need to do?

Best Regards,

Xingyu Zhu