hi,

In the current project, we use ADS5560 whos sampling rate is 30.72MHz, and the sampled data is transferred to Spartan6 through DDR LVDS parallel port.

the sample clock signal into ADS5560 is generated by CDCE72010, and AC coupled through a transformer. The differential clock after the transformer and before

ADS5560 is shown as follows,

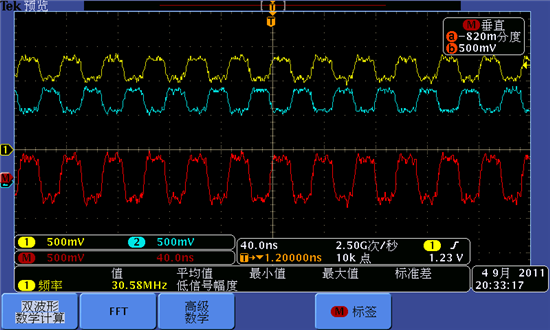

The DDR data line pair is shown as follows

but the clock signal of ADS5560 output is distorted very severely, whos duty cycle is far from 50%. the pcb board ground plane is spilt into AGND and DGND sub-plane. ADS5560 is mounted on AGND, and Spartan on DGND. Ground plane may cause impedance discontinuity, but the degree of effect is unkonw now, and the data line pair seem to work well, since that the problem clock line pair may have no relation to the split. what is the possible cause?