I'm working on a new project and I'm trying to use the PCM5122 DAC clocked by a 12 MHz oscillator as I2S master (the DAC generates BCK and LRCK signals). My goal is to achieve what stated at page 22 of PCM5122 datasheet which says:

"SCK rates that are not common to standard audio clocks, between 1MHz and 50MHz, are only supported in software mode by configuring various PLL and clock-divider registers. This programmability allows the device to become a clock master and drive the host serial port with LRCK and BCK, from a non-audio related clock (for example, using 12MHz to generate 44.1kHz (LRCK) and 2.8224MHz (BCK) )."

so I think it should be possible if it's reported as example on the datasheet.

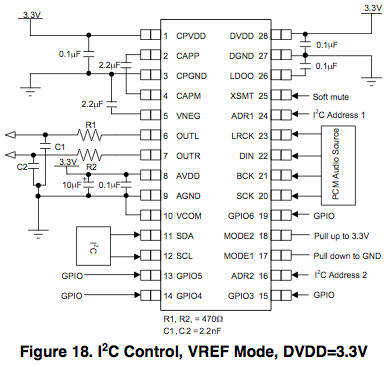

I'm using the DAC as shown on page 17 of the datasheet:

with a 12 MHz oscillator connected to the pin 20 (SCK).

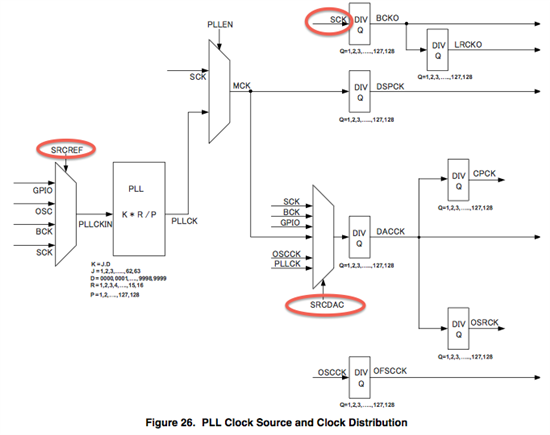

In order to get proper audio clocks from a 12 MHz oscillator we have to use the internal PLL so I put an eye on Figure 26 of the datasheet (page 24)

and found some troubles:

1) How it's possible to generate precise BCK and LRCK from a 12 MHz source if BCK and LRCK outputs are generated from SCK only?

BCK and LRCK dividers should be clocked by the PLL output not directly from SCK. In fact I'm only able to generate LRCK and BCK by dividing the 12 MHz SCK leading to unprecise results. I'm sure I'm missing something.

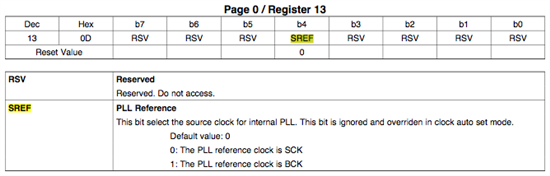

2) SRCREF register is meant to select the clock input for the PLL between 4 different possibilities. If you look at register 13 description (page 81 on the datasheet) you got simply the bit 4 that le you choose between SCK and BCK as PLL clock input

Finally page 23 says:

"The source reference clock for the PLL reference clock is selected by programming the SRCREF value on Page 0, Register 13, D(6:4)."

reporting to use bits 6 to 4 of register 13 to set the PLL input (how?). I'm confused, someone knows wich is the truth?

3) In figure 26 there is a SRCDAC to route clock to DAC, charge pump and digital filter modules. The point here is that SRCDAC register does not exists or is completely missing from the documentation. So, the question is, where the DACCK comes from?

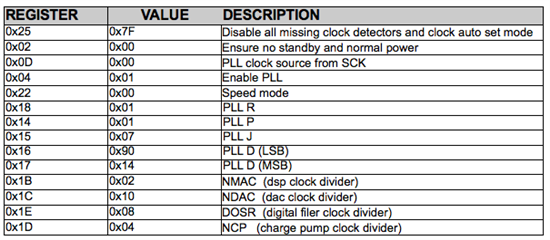

Even with the above problems I did my best to let the PCM5122 acting as I2S master using PLL mode (trying to play at 44100 KHz 16 bit). The registers config I'm using without success are the following:

I got 12 MHz output on both LRCK and BCK (leaving their dividers as 0x00) and no CPCK. If I set the BCK and LRCK dividers to values different from 0 I got 990.312 KHz as charge pump clock.

The clock is obviously not correctly routed and the PLL is not clocking the LRCK and BCK signals but I'm not able to see what's wrong (please note that I'm using values from datasheet example to set PLL coefficients P, J and D).

Sorry for the very long post, I hope someone is able to fill the holes in the datasheet as TI support told me to report my problems on the forum!

Thanks in advance

Best Regards

Marco