Hi all,

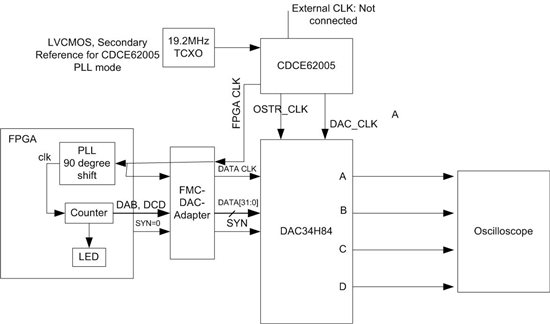

I encountered some problems when testing the dac34h84evm. The DAC board is connected with the Xilinx VC-707 FPGA board using the FMC-DAC-adapter.

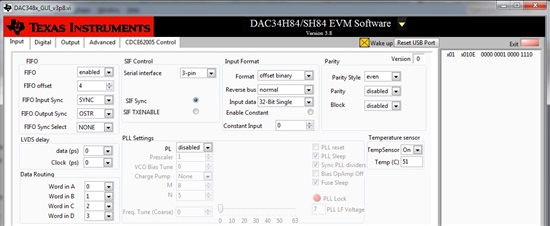

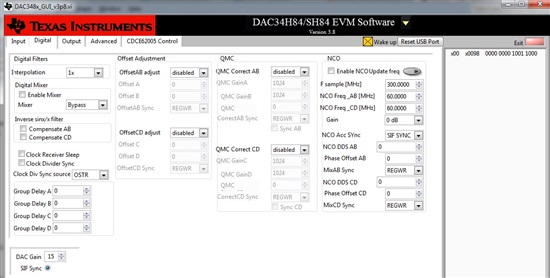

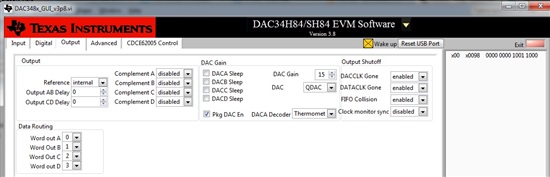

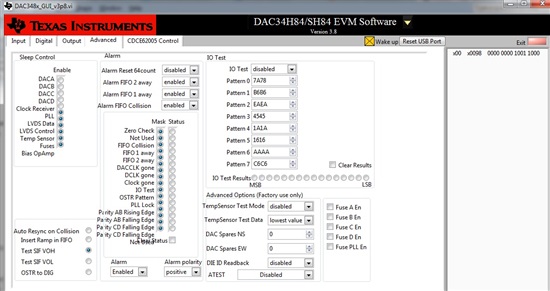

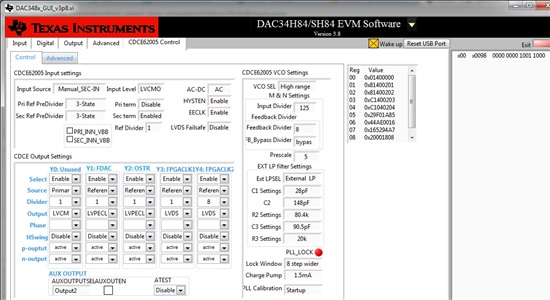

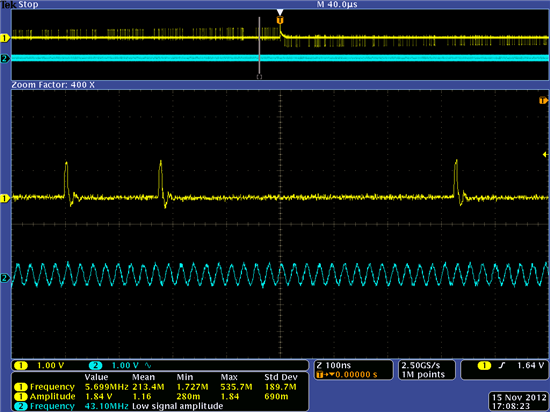

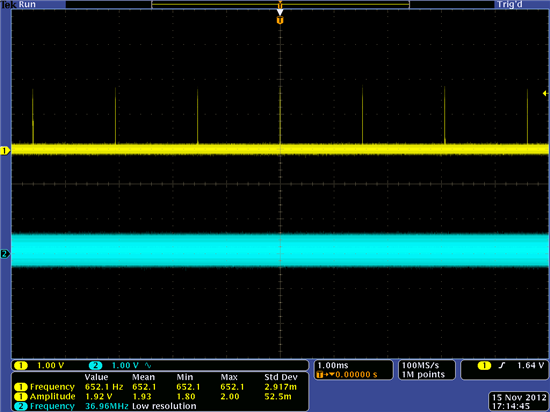

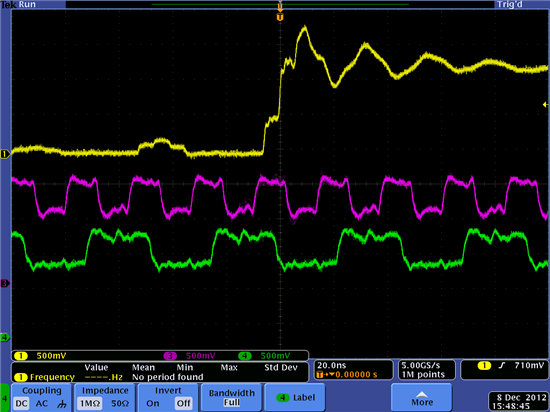

The clock for data (DCLK) is from the CDCE62005 whose frequency is 19.2 MHZ, the same as DAC's input clock (DAC_CLK). Data is center-aligned. We use the software(DAC348x EVM Software GUI (Rev. B) ) to configure it. Only FIFO is enabled and x1 interpolation. But we don't get the analog output on the oscilloscope. Whatever data we input. i.e. DA=DA+1 or constant value, we get nothing but some pulses.

I checked the connection of FMC on FPGA to FMC-DAC adapter which is correct, so i don't think the input "DA" is wrong. So I don't know exactly what goes wrong. Please help. You can reach me at jamesfade_1234@hotmail.com or this reply. Thanks a lot.

I attach my VHDL interface code.

--===================================

-- intf_TI_dac34h84evm

-- Description: This module is used to connect with FPGAs with HSMC port for Terasic ADA

-- (1) data is center-aligned.

--==================================

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

-- obufds library

Library UNISIM;

use UNISIM.vcomponents.all;

library work;

entity intf_TI_dac34h84evm is

port (

FPGAOUT_CLKP_I : in std_logic;

FPGAOUT_CLKN_I : in std_logic;

--PARITYP : out std_logic; --PARITYABP: Sync the FIFO pointer or act as a parity input for the AB-data bus

--PARITYN : out std_logic;

SYNCP : out std_logic; --SYNCP: allow complete reversal of the data interface when setting the rev_interface bit in register config.

SYNCN : out std_logic;

-- FIFO_ISTRP : out std_logic; --ISTRP: act with SYNC, PARITY.

-- FIFO_ISTRN : out std_logic;

DATA_CLKP : out std_logic; --DATACLKP: LVDS positive input data clock. Data are lutched on both edges of DATACLKP/N.

DATA_CLKN : out std_logic;

IO_DAP : out std_logic_vector (15 downto 0); --DAB: data for AB-channel

IO_DAN : out std_logic_vector (15 downto 0);

IO_DBP : out std_logic_vector (15 downto 0); --DCD: data for CD-channel

IO_DBN : out std_logic_vector (15 downto 0)

);

end intf_TI_dac34h84evm;

Architecture Behavior of intf_TI_dac34h84evm is

------------ components ------------

component pll_div is

port(

clkin : in std_logic;

rst : in std_logic;

pwrdwn : in std_logic;

clkout0: out std_logic;

clkout1: out std_logic;

clkout2: out std_logic;

clkout3: out std_logic;

clkout4: out std_logic;

clkout5: out std_logic

);

end component pll_div;

------------

signal clk : std_logic;

-- signal PARITY : std_logic;

signal SYNC : std_logic;

-- signal FIFO_ISTR : std_logic;

signal DATA_CLK : std_logic;

signal IO_DA : std_logic_vector (15 downto 0);

signal IO_DB : std_logic_vector (15 downto 0);

signal clkin : std_logic;

signal FPGAOUT_CLK : std_logic;

begin

--=======================================================

-- Dac34h84evm outputs

--=======================================================

--PARITY

-- OBUFDS_inst_PARITY : OBUFDS

-- generic map (

-- IOSTANDARD => "DEFAULT")

-- port map (

-- O => PARITYP,

-- OB => PARITYN,

-- I => PARITY

-- );

--SYNC

OBUFDS_inst_SYNC : OBUFDS

generic map (

IOSTANDARD => "DEFAULT")

port map (

O => SYNCP,

OB => SYNCN,

I => SYNC

);

--FIFO_ISTR

-- OBUFDS_inst_FIFO_ISTR : OBUFDS

-- generic map (

-- IOSTANDARD => "DEFAULT")

-- port map (

-- O => FIFO_ISTRP,

-- OB => FIFO_ISTRN,

-- I => FIFO_ISTR

-- );

--DATA_CLK

OBUFDS_inst_DATA_CLK : OBUFDS

generic map (

IOSTANDARD => "DEFAULT")

port map (

O => DATA_CLKP,

OB => DATA_CLKN,

I => DATA_CLK

);

--IO_DA

IO_DA_GEN: for j in 0 to 15 generate

begin

OBUFDS_inst_IO_DA : OBUFDS

generic map (

IOSTANDARD => "DEFAULT")

port map (

O => IO_DAP(j),

OB => IO_DAN(j),

I => IO_DA(j)

);

end generate IO_DA_GEN;

-- IO_DB

IO_DB_GEN: for j in 0 to 15 generate

begin

OBUFDS_inst_IO_DB : OBUFDS

generic map (

IOSTANDARD => "DEFAULT")

port map (

O => IO_DBP(j),

OB => IO_DBN(j),

I => IO_DB(j)

);

end generate IO_DB_GEN;

IBUFDS_inst_FPGAout_clk : IBUFDS

generic map (

DIFF_TERM => FALSE, -- Differential Termination

IBUF_LOW_PWR => TRUE, -- Low power (TRUE) vs. performance (FALSE) setting for refernced I/O standards

IOSTANDARD => "DEFAULT")

port map (

O => FPGAOUT_CLK,

I => FPGAOUT_CLKP_I,

IB => FPGAOUT_CLKN_I

);

-------------------

-- signals setup --

-------------------

-- clk is 90 degree in advance than DATACLK, so IO_DA and IO_DB is prepared before the rising edge of DATA_CLK

pll: pll_div

port map(

clkin => FPGAOUT_CLK,

rst => '0',

pwrdwn => '0',

clkout4 => clk

);

SYNC <= '0';

DATA_CLK <= FPGAOUT_CLK;

proc_counter: process(clk)

begin

if(clk'event and clk='1') then

IO_DA <= IO_DA+1;

end if;

end process proc_counter;

end Behavior;