I have read the ads1298.PDF very carefully.I config the MCBSP in SPI mode currently,and currect.

on the other hand ,i followed the ADS1298 inital sequence,sending the command order or giving the high and low level to some IO pins.

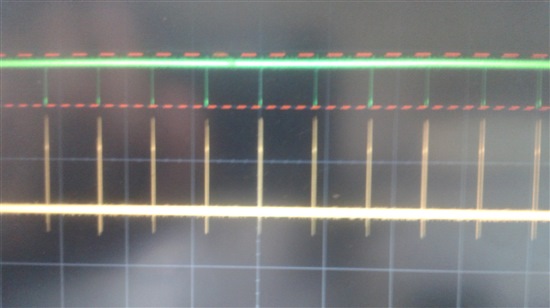

however,although my DRDY has signals out, I couldn't get the clk out . Also i didn't get the reference voltage.

So how could this happen?

Is there some help me ?

i have already read some post here . But they all used the SPI interface of their MCU directly.i tried to use the STM32 spi interface to communicate with ADS1298.that is ok.

I just don't know what is wrong in my project ? that problem has puzzled me for morths.

Wish someone have done this already,very appreciate for your help.

-----------picture 1

-----------picture 1 -------picture2

-------picture2 ------picture3

------picture3 ------picture4

------picture4 -----picture5

-----picture5 ------picture6

------picture6