Using F28335 development kit (mixing C and C++), in one application and an OMAP (pure C++) with both ARM and DSP in another, all with CCS v5.

It appears that there may be a problem with the TI C/C++ compiler or with CCS when "extern C" is used to bring in C code for "interrupt void TINT0(void)", and all other ISRs, into C++.

GeorgeM composed the following TI Wiki entry in 2008 but he has no entries on the TI community prior to Oct 2008 and apparently none on this subject since:

http://processors.wiki.ti.com/index.php/Invoke_a_C%2B%2B_Class_Member_Function_from_an_Interrupt

I have implemented this solution with unacceptable results. I need a resolution that includes a statement that the Syntax error is inconsequential, i.e., a CCS bug that has no further consequences, or a quick bug fix, or a different solution ot mixed C and C++ that allows interrupts to be called from C++. The latter option is preferable.

Actually I did not have to implement anything since "extern C" is already used in DSP2833x_DefaultIsr.h which accompanies DSP2833x_DefaultIsr.c .

But when a copy of these files are renamed as hpp and cpp files and called by a Main in a cpp file, Syntax errors pop up - these is not the first YI-provided files in my use of the FlashingLeds example to be converted to C++ with success; and I have already integrated successfully my own C++ code that is relatively complex (using templates).

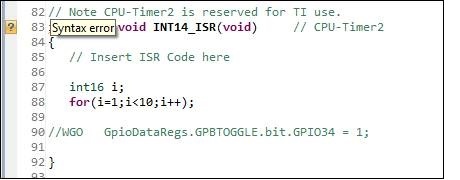

The Syntax errors affect neither the success of the compilation nor the apparent success of execution, but the errors/warning leave a bad feeling that the implementation may be unreliable.

The result from following the paradigm described in GerorgeM’s post is the Syntax error that I get in CCS – it is unacceptable to have a Syntax error flagged in the IDE which nevertheless appears to have no affect on the compilation or execution – compilation or execution both seem to be something that can be accomplished but with unknown reliability.

I have tried pragma interrupt, with no success. I have tried __interrupt without use of a pragma (note: 2x underscores), with no success.

The latter does not fix the Syntax error, but changes the view in CCS, in that the left margin is now hi-lited light blue, as shown in one of the following images.

Here is a list of screen captures as an exhibit that there are no compiler errors, and that there are syntax error warnings shown in the CCS Console, though they appear in the file listing pane.

CPP Syntax error

Syntax error warnings in C++ files using extern C on the functions

pragma interrupt error

"__pragma interrupt" Syntax error warning with blue hi-lited left margin

HPP Syntax error warnings using extern C - also Console shows no new errors with additional compile after previous compile

Console showing no associated errors or warnings after fresh compile of HPP which is displayed by CCS with Syntax error warnings

No H Syntax error warnings using extern C - fresh compile with function declarations commented out of C++/H++ Default_Isr.cpp/hpp

Console showing No associated errors or warnings after fresh compile of H which is displayed by CCS with No Syntax error warnings