My customer needs to fix their issue below ASAP:

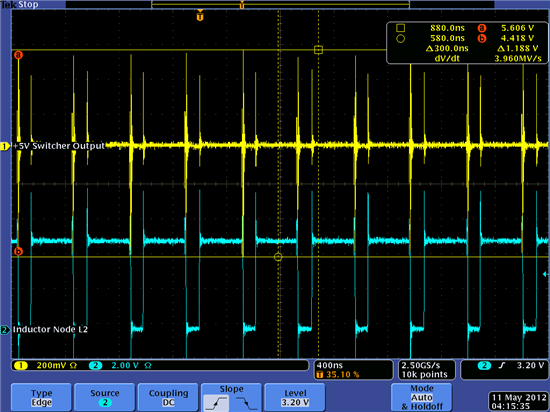

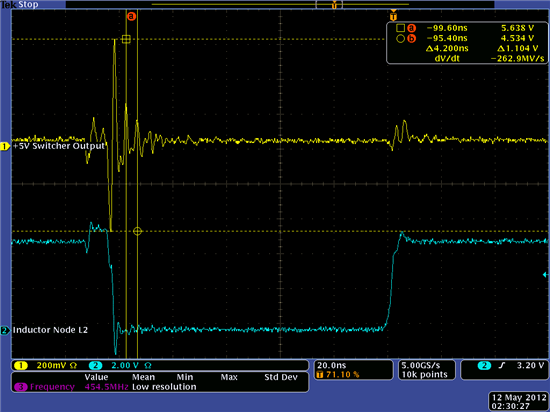

We are now in the process of doing validation testing on the hardware for this project. We have a new issue with the TPS63020 power supply chip and we could use some help from TI. The problem we have is excessive ringing during switch cycles in boost mode with the supply. Power Save mode is off so the device is in continuous operation mode. I have attached some scope traces that show the output. Since we are operating in Boost Mode (3.0 to 4.4V input, 5V output), I expect that the primary contributors to the overshoot are the two FETs connected to inductor node L2. The other two FETs should be continuously ON or OFF at all times during operation.

I have been looking at using a snubber circuit to damp these oscillations, but I would like to know a few things:

1) What is the expected parasitic capacitance of each of the power FETs? This would help me get an estimation of the capacitor I need to use for my snubber.

2) I have never designed a snubber for a synchronous boost switcher before. I assume that I need to consider the combined parallel capacitance (and associated inductance) of the two switching FETs in my design. Can you confirm this to be the correct approach?

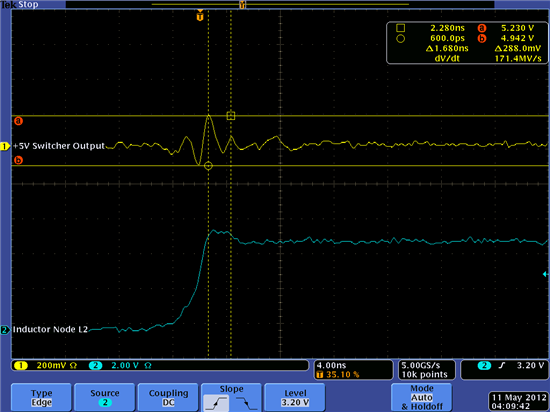

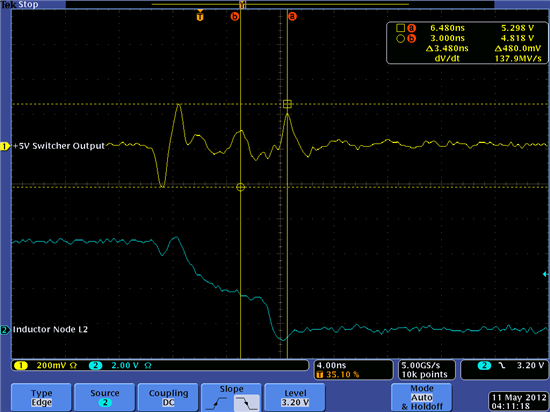

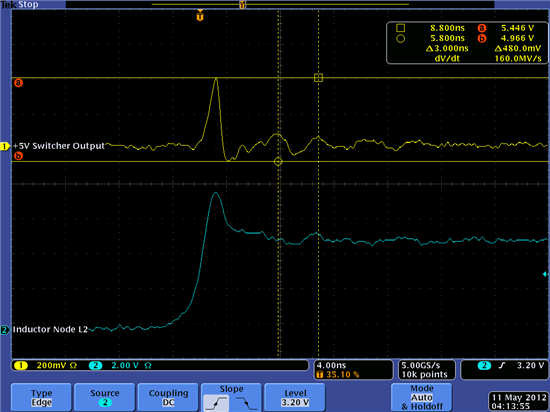

3) I have attached some scope traces of the output ringing in conjunction with the switch voltage at node L2. The output noise was measure with an active probe and a very low inductance ground lead (1.5cm). I observe that the oscillation at the switch point is significantly worse when the L2 node is being switched to GND (falling edge) as compared to the rising edge. Is there an explanation for this based on the switching operation? I assumed based on duty cycle that the current through the FET to GND is higher than the current through the FET to output.

Switching Noise at +5V Boost Output

Rising Edge Unloaded

Falling Edge Unloaded

Rising Edge with 500mA Load

Falling Edge with 500mA Load

Thanks!