Part Number: TDA4VM

How to run OpenVX Host on R5F and a node to run on A72 (Linux) as target?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TDA4VM

How to run OpenVX Host on R5F and a node to run on A72 (Linux) as target?

The initial reference to this topic i.e. OpenVX host on R5F could be found in the below appnote

Note:

This is just a proof of concept and TI has no plans currently to integrate this feature into the SDK.

The patches are created on RTOS SDK 08_06_00_09 and Linux SDK 08_06_00_11 on TDA4VM.

The current limitations with this implementation are mentioned at the end of this document.

Customer can test this feature on the above said SDK versions.

Porting the patches to the later versions of SDK is currently not a part of TI's plan.

As the app note currently consists of patches from SDK 8.1, Please find the same patches below for SDK 8.6.

The below patches have been ported from SDK 8.1 to SDK 8.6

Please follow the steps mentioned in the AppNote to apply these patches.

After applying the above patches, please apply the below mentioned patches in their relevant folders to enable the A72 as target feature.

/cfs-file/__key/communityserver-discussions-components-files/791/A72_5F00_target_5F00_tiovx.patch

Apply the above patches in vision_apps and tiovx folders respectively.

Step 1: Un-comment the application you would like to run in ${PSDKRA}/vision_apps/platform/j721e/rtos/common/app_run.c (eg. to run the multi-cam application, uncomment the function app_multi_cam_main())

Step 2: Rebuild the SDK and flash the SD Card as mentioned in the above steps.

Step 3: Boot the EVM and login as "root"

Step 4: On the EVM, do below steps to init the environment for the demos

cd /opt/vision_apps source ./vision_apps_init.sh

The A72 based application flow is as follows

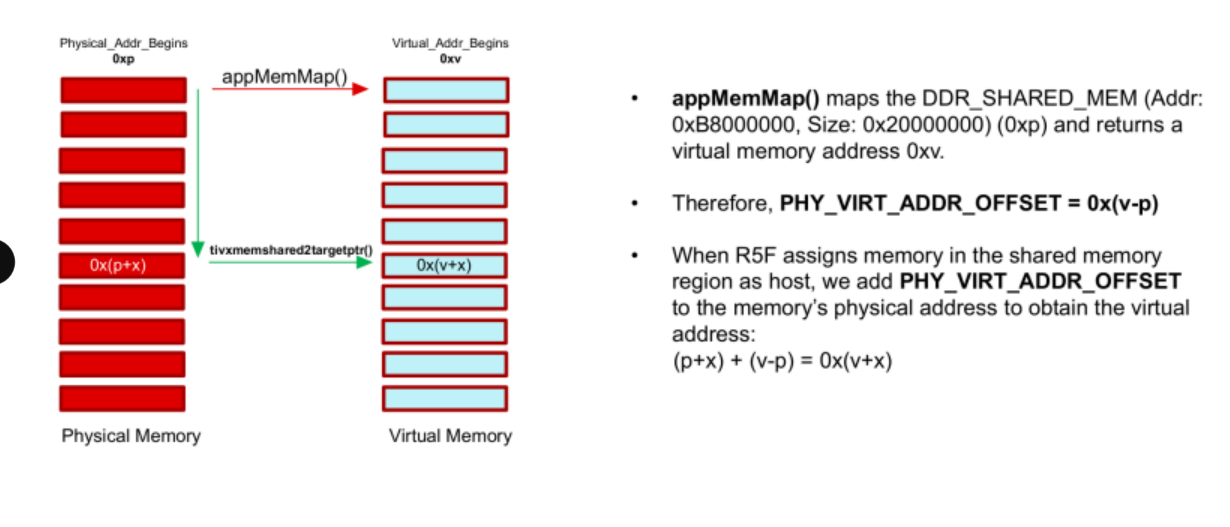

Step 1: Does the memory initialization on A72 by doing a mmap to the DDR_SHARED_REGION to obtain the virtual address and the offset required is calculated.

Step 2: A72 as target is configured and intialized in the OpenVX Framwork.

Step 3: Does the target side intializations of the kernels that uses A72 as target.

Step 4: Sends a dummy IPC notifications to the cores that would communicate to A72 in the future. During this IPC transfer, the endpoint of A72 is stored by the cores (to be used later for IPC communication to A72)

Step 5: Sends the trigger to MCU2_0 (R5F) to run the application.