Other Parts Discussed in Thread: TDA4VH

How to enable the USB 3.0 functionality on lane 3 of J784S4 evm?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TDA4VH

How to enable the USB 3.0 functionality on lane 3 of J784S4 evm?

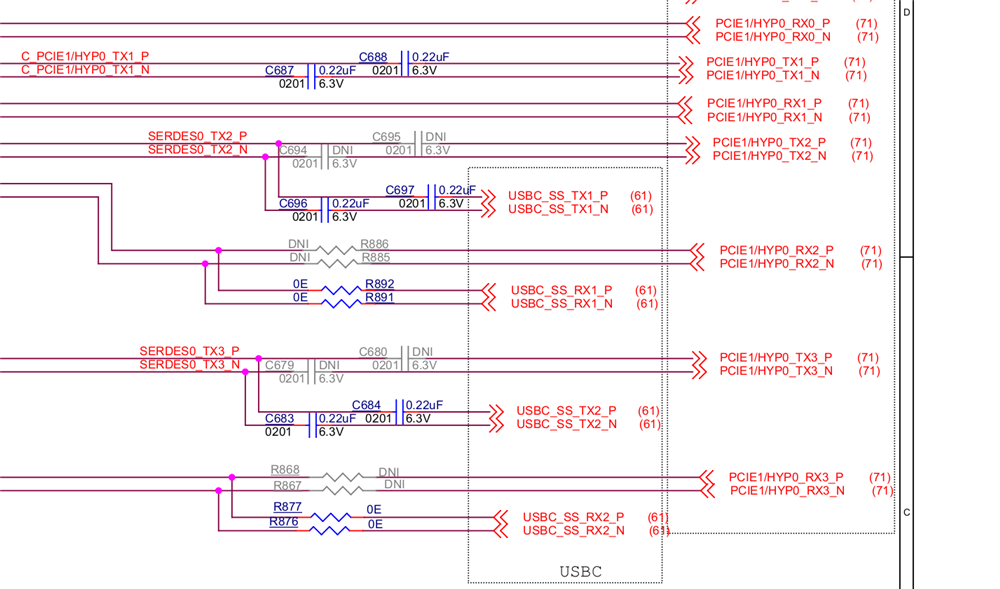

On TDA4VH We have two lane connected to the TYPEC.

But in the dtsi we are only configuring the lane 3 for USB3.0 Support.

To enable the USB3.0 lane functionality on lane 2 , you need to do the below changes.

diff --git a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

index 492975144..94e6f7702 100644

--- a/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

+++ b/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@ -711,13 +711,12 @@ serdes0_pcie_link: phy@0 {

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz0 1>, <&serdes_wiz0 2>;

};

-

- serdes0_usb_link: phy@3 {

- reg = <3>;

- cdns,num-lanes = <1>;

+ serdes0_usb_link: phy@2 {

+ reg = <2>;

+ cdns,num-lanes = <2>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_USB3>;

- resets = <&serdes_wiz0 4>;

+ resets = <&serdes_wiz0 3 >,<&serdes_wiz0 4>;

};

};

@@ -780,7 +779,7 @@ &main_navss_intr {

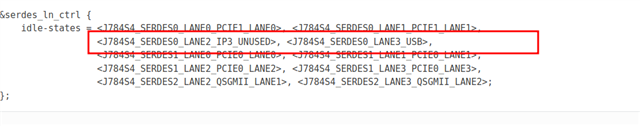

&serdes_ln_ctrl {

idle-states = <J784S4_SERDES0_LANE0_PCIE1_LANE0>, <J784S4_SERDES0_LANE1_PCIE1_LANE1>,

- <J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>,

+ <J784S4_SERDES0_LANE2_USB_SWAP>, <J784S4_SERDES0_LANE3_USB>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>, <J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>, <J784S4_SERDES1_LANE3_PCIE0_LANE3>,

<J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>;

@@ -1229,11 +1228,6 @@ &main_mcan16 {

phys = <&transceiver3>;

};

-&serdes_wiz0 {

- typec-dir-gpios = <&wkup_gpio0 28 GPIO_ACTIVE_HIGH>;

- typec-dir-debounce-ms = <700>; /* TUSB321, tCCB_DEFAULT 133 ms */

-};

-

&usb_serdes_mux {

idle-states = <0>; /* USB0 to SERDES lane 3 */

};

diff --git a/include/dt-bindings/mux/ti-serdes.h b/include/dt-bindings/mux/ti-serdes.h index 91ea9633c..5a6ac4587 100644 --- a/include/dt-bindings/mux/ti-serdes.h +++ b/include/dt-bindings/mux/ti-serdes.h @@ -131,7 +131,7 @@ #define J784S4_SERDES0_LANE2_PCIE3_LANE0 0x0 #define J784S4_SERDES0_LANE2_PCIE1_LANE2 0x1 -#define J784S4_SERDES0_LANE2_IP3_UNUSED 0x2 +#define J784S4_SERDES0_LANE2_USB_SWAP 0x2 #define J784S4_SERDES0_LANE2_IP4_UNUSED 0x3 #define J784S4_SERDES0_LANE3_PCIE3_LANE1 0x0

Save the above change do

cd <linux-sdk>

make linux-dtbs

cp board-support/<linux-*>/arch/arm64/boot/dts/ti/k3-j784s4-evm.dtb /media/<xyz>/rootfs/boot

NOTE:After doing above changes USB will work in 2.0 mode only if you are using lane 3

Regards

Diwakar