Part Number: J784S4XEVM

Tool/software:

How to load TIFS using JTAG on HS-FS device?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

On HS-FS device , JTAG for M4 core will locked by default so there is no way to load the TIFS binary to M4_0 using JTAG in No-Boot mode.But if you still want to load the TIFS using JTAG there is another way for it, using Dev-Boot mode

During the Development boot (BOOTMODE[4] = 0), the SMS ROM code will act as the boot of the primary image completion, and the SMS ROM will then be waiting for firmware load message from MCU R5. Thus as user you can load a standard u-boot/SPL image to the R5 RAM. U-boot/SPL will then load the SMS firmware and complete the full boot.

We will add the TIFS binary along with the SBL image and then using JTAG we will load the SBL image on the R5 core. As SBL already have TIFS embedded in it, no need to read it from the external boot media, we will just pass the pointer of the TIFS binary to the secure ROM, so that it can authenticate and load it.

Steps to build the SBL embedded with TIFS

In the PDK we do have TIFS binary in the .h format along with .bin

for example in J784S4 RTOS SDK you can find the HS-FS TIFS header file at:

<RTOS_SDK>/<pdk>/packages/ti/drv/sciclient/soc/V6/sciclient_firmware_V6_hs_fs_enc.h

This .h file can be included in the SBL image.

Please have a look at the patch for the implementation on J784S4 9.2 RTOS SDK.

/cfs-file/__key/communityserver-discussions-components-files/791/0001_2D00_Embedded_2D00_TIFS_2D00_into_2D00_SBL_2D00_binary.patch

Keep the Device in Dev Boot mode and power on .

For EVM DIP switch configuration as follow’s

SW8[1:8] 1000_0000

SW9[1:8] 0111_0000

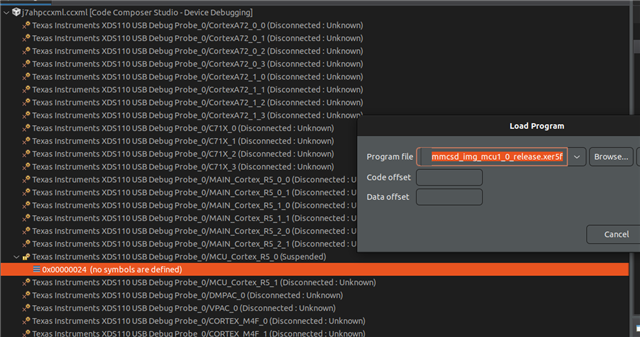

Open debugger connect to R5 core , load SBL image and run.

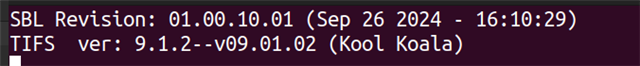

UART console print:

With this approach we are not actually connecting to the M4_0 for loading TIFS but SBL is doing the task for us.You can also do the power on of the other core's inside the SBL using TISCI api, so that you can load the firmware on those core using JTAG at later stage.