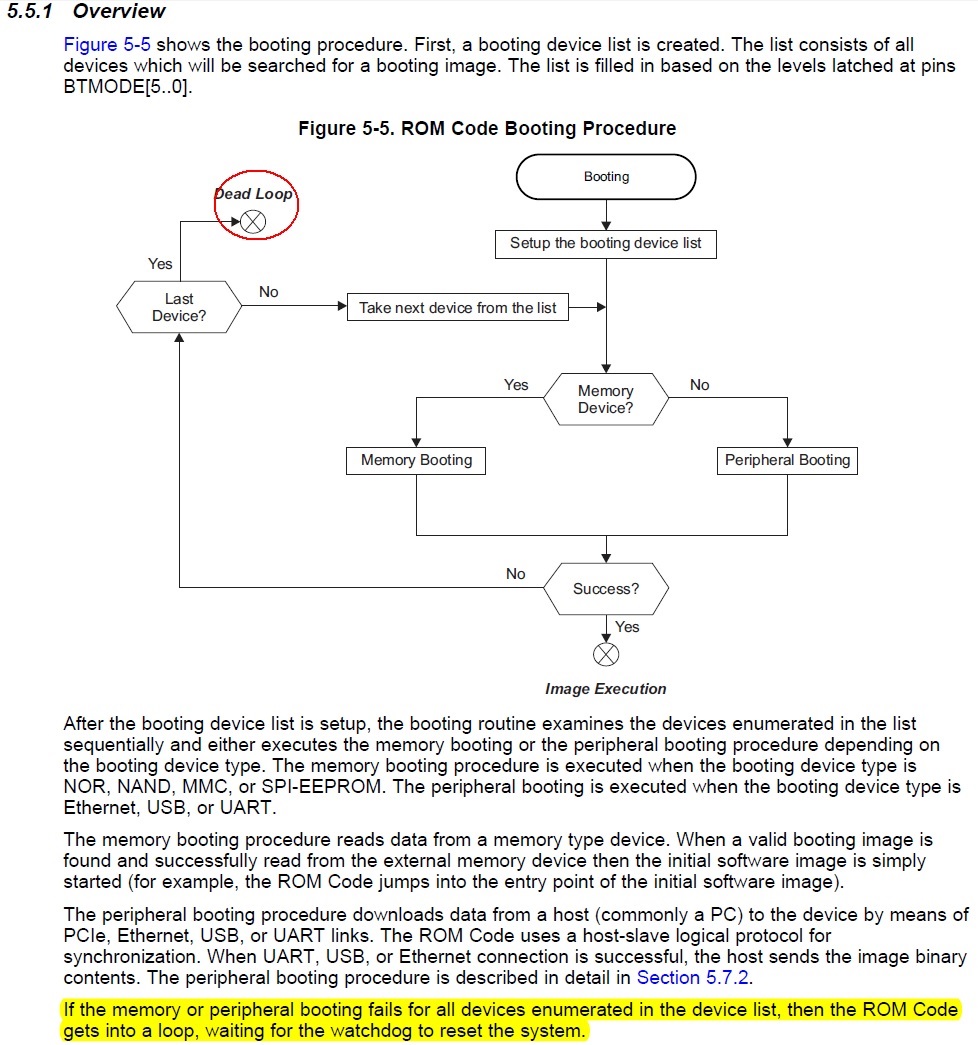

as below description, I understand after BOOTLOADER scan the device list set by bootmode, the BOOTLOADER will enter dead loop and waiting for watchdog(3 minutes) reset. But from test result seems the BOOTLOADER scan the device list in endless loop, for example I set bootmode[5:0] = 111110b, all device in the list are empty, UART0 output CCCCCCCC consequently, never stop, so I think the watchdog never overflow.

So please help check ROM code if below description is not accurate.