Other Parts Discussed in Thread: SYSBIOS, AM5749, AM5728

Tool/software: TI-RTOS

Hi TI Experts,

Please let me confirm the following question.

Now we met two issues while the SMP and multi-core debug. Would you please teach me the workaround for this?

No.1 : SMP Debug issue

Not work the Cross-Trigger in case of using the AM574x IDK. Here is the reproduced way.

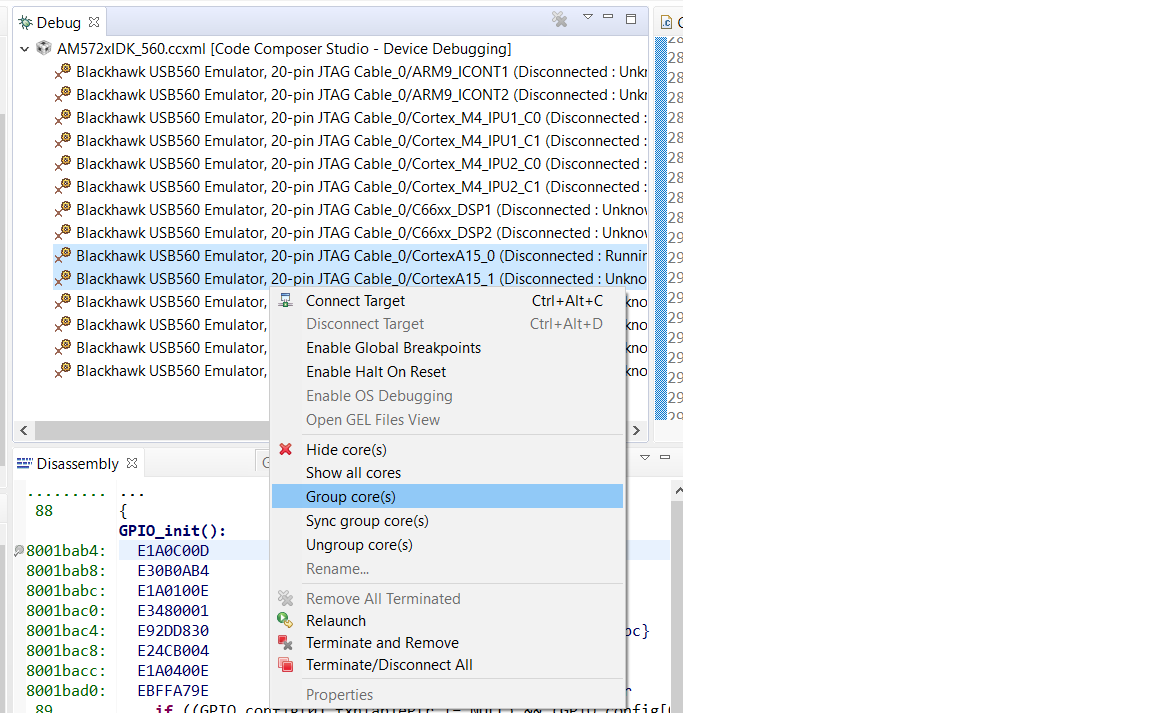

1. Sync Group the Target the A15_0 and A15_1

2. Connect the target

3. Load the program for each core.

4. Run the program.

Note: When I used the AM572xIDK, it was worked well.

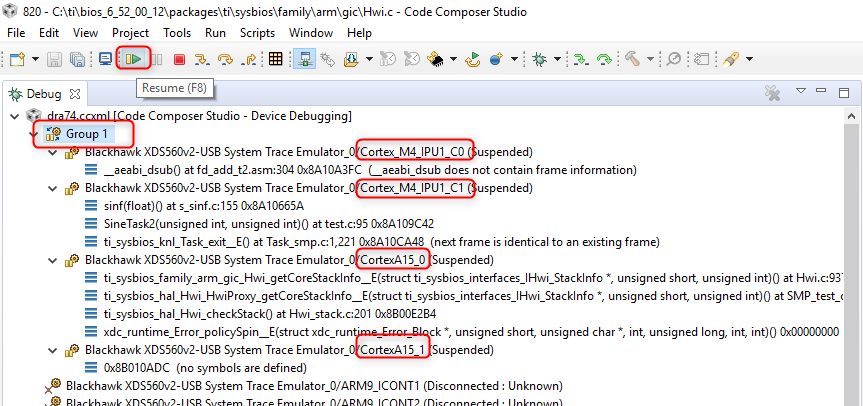

No.2 : Sync Group issue

When connected A15 cores with sync group, the group was forced release the sync group. And when re-select the sync group, it showed the following error in case of using AM574xIDK.

******************

CortexA15_0: Trouble configuring cross triggering: Error enabling this function: There is no AET resource to support this job.

CortexA15_1: Trouble configuring cross triggering: Error enabling this function: There is no AET resource to support this job.

******************

In addition to this, when connected the A15_0 core and IPU1_C0 at first and selected the sync group, it also showed the same error in case of using the AM574xIDK.

Note: When used the AM572xIDK, we did not meet this issue.

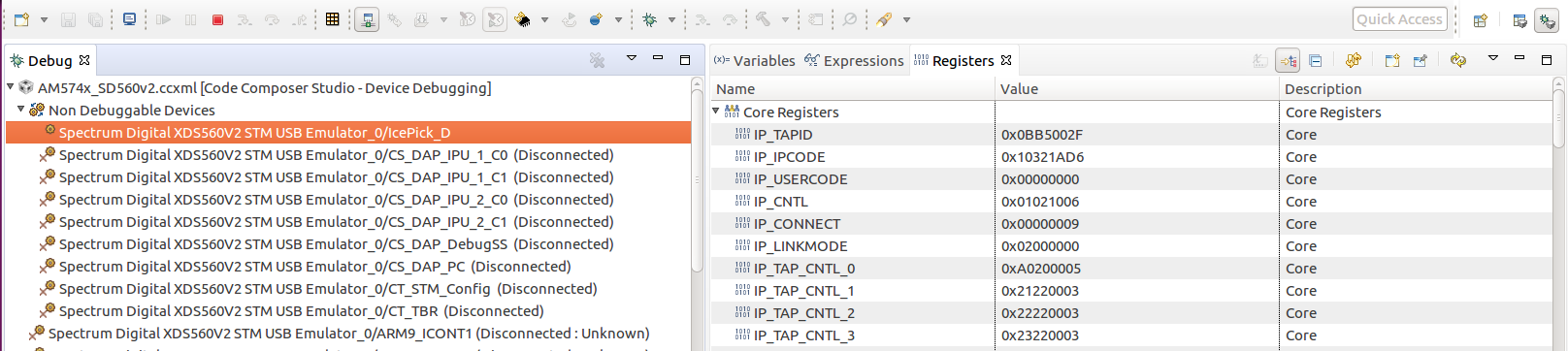

No.3 : A15 and M4 SMP debug

When tried to do the debug with SMP code for A15 and SMP code for M4 debug at the same time, it could not work.

If you have any questions, please let me know.

Best regards.

Kaka