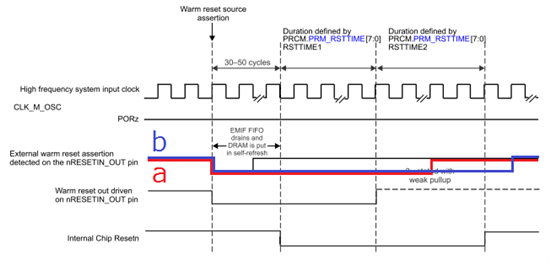

Must the external warm reset be asserted during at least 30 cycles?

Must not the external warm reset continue being asserted until the duration defined by RSTTIME2 bit field?

Must not the external warm reset be asserted (goes low) during the duration defined by RSTTIME2 bit field?

AM335x ARM Cortex-A8 Microprocessors (MPUs) Technical Reference Manual (Rev. G)

http://www.ti.com/lit/ug/spruh73f/spruh73f.pdf

8.1.7.4.1 External Warm Reset

8.1.7.4.1.2 Warm Reset Sequence

Best regards,

Daisuke