Other Parts Discussed in Thread: AM3359, SYSBIOS

Hello,

I am using a am3359 processor interfaced with a fpga.

I have write a fpga driver to initialize the Gpmc bus: Cs0, Nor flash like, asynchronous, 16 bits, address and data multiplexed, no wait pin.

It's ok now to read and write datas. We have improved the timing by using a scope: 60ns for an word read access and 40ns for a write access.

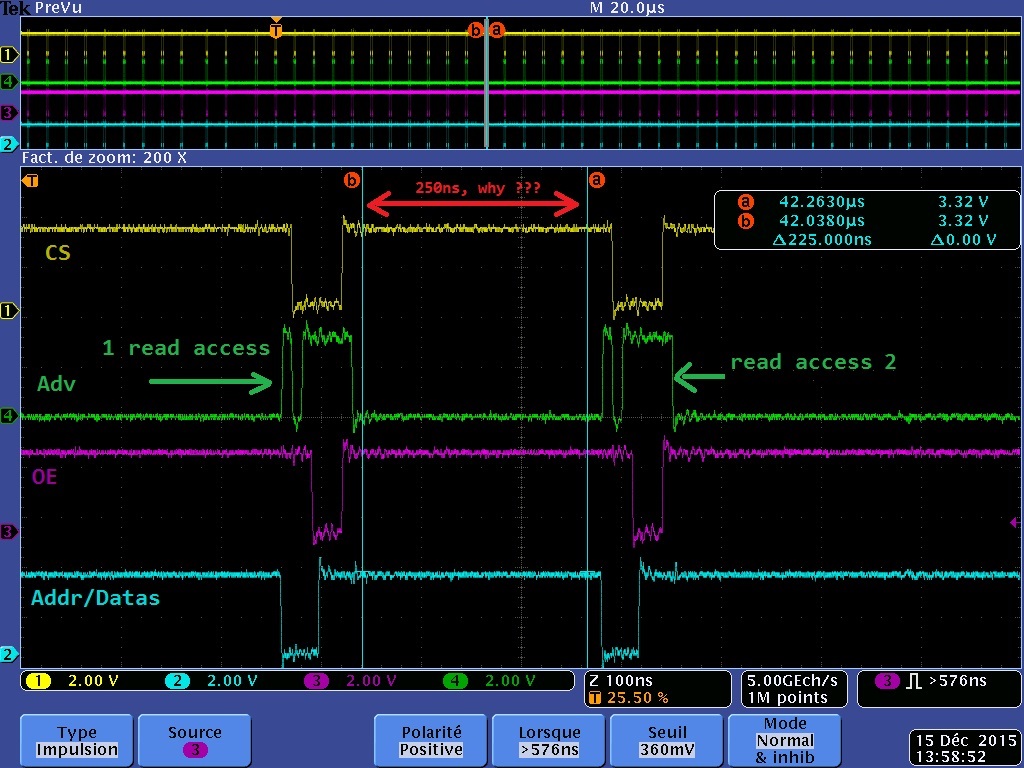

My problem: if i make two consecutly access ( 2reads or 2 write), impossible to decrease the duration between two access: this operation take 250ns.

My code :

volatile unsigned short toto;

toto = (*((volatile unsigned short *)( FPGA_CS0_BASEADDR + offset)));

toto = (*((volatile unsigned short *)( FPGA_CS0_BASEADDR + offset)));

The result (scope), you can the the 'bad' delay : 250ns

It's very important for me to optimize the read access (get a 64 bits value in fpga registers in 4 read access)

I have tried to decrease the GPMC_CONFIG6_0 field value without success..

I have also tried to configure the GPMC in burst mode multiple :

- GPMC_CONFIG1_0 : READMULTIPLE = GPMC_ACCESSTYPE_SINGLE

- GPMC_CONFIG1_0 : ATTACHEDDEVICEPAGELENGTH = GPMC_DEV_PAGELENGTH_FOUR (4*16)

I have tried to decrease, increase - GPMC_CONFIG6_0 field without result: CYCLE2CYCLESAMECSEN, CYCLE2CYCLEDELAY, BUSTURNAROUND...

I dont think that it is due to an interruption who disturb the read code.

Can you help me, have you an idea please ?

Thank you

JM