Hi I actually have a 8 and 16 bit gpmc memory maped region connected to fpga.

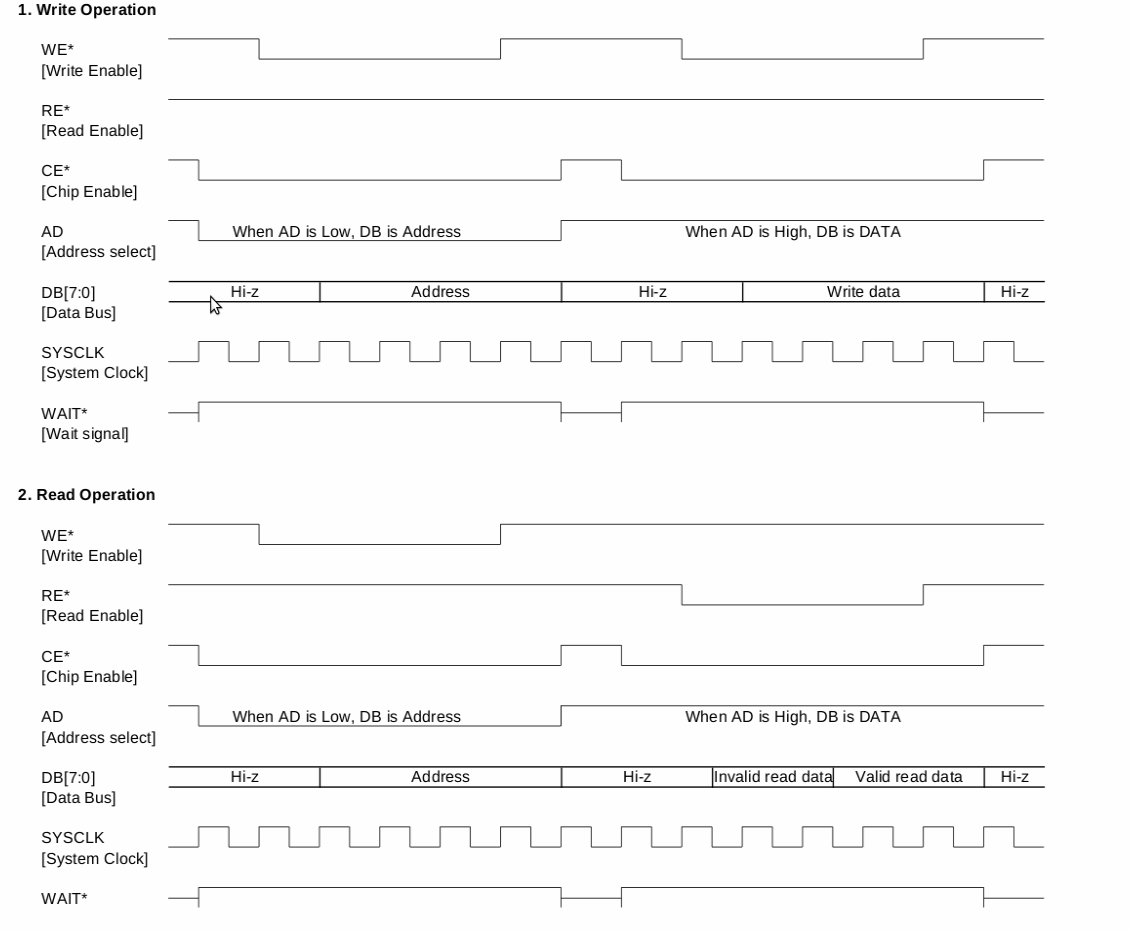

my question is how do i go about writing to individual registers within the external devices. say for example i have fpga1 connected to cs region 2 with a base address of 0x02000000 and a size of 10000000. how do i send the register address and the value needed to be written to that register address within the cs region.

how do i go about reading back from that individual register to which i wrote the data to.

Regards

-Parker