Part Number: AM3352

Hello,

I and my customer would like to improve GPMC read access time.

The primary GPMC configuration is like follows..

gpmc_config1

READMULTIPLE : 0h = single access

READTYPE : 0h = Read Asynchronous

WRITEMULTIPLE : 0h = Single access

WRITETYPE : 0h = Write Asynchronous

DEVICESIZE : 1h = 16 bit

DEVICETYPE : 0h = NOR Flash like, asynchronous and synchronous devices

MUXADDDATA : 0h = Non-multiplexed attached device

TIMEPARAGRANULARITY : 0h = x1 latencies

GPMCFCLKDIVIDER : 0h = GPMC_CLK frequency = GPMC_FCLK frequency

gpmc_config2

CSWROFFTIME : 8

CSRDOFFTIME : 8

CSEXTRADELAY : 0

CSONTIME : 0

gpmc_config4

WEOFFTIME : 6

WEONTIME : 4

OEOFFTIME : 6

OEONTIME : 4

gpmc_config5_reg

RDACCESSTIME : 6

WRCYCLETIME :10

RDCYCLETIME :10

gpmc_config6_reg

CYCLE2CYCLEDELAY : 4

CYCLE2CYCLESAMECSEN : 1

CYCLE2CYCLEDIFFCSEN : 1

StarterWare sample code:

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

dummy_data = *(volatile uint32_t *)(0x8000000);

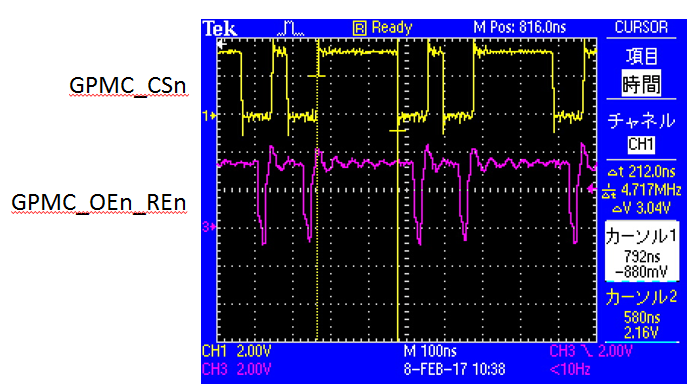

Wave form:

CS on and off, OE on and off of waveform looks OK, but cycle2cycle is not good.

CYCLE2CYCLEDELAY of program is 4 but cycle2cycle of waveform is 212 ns.

So my target is shorten the cycle2cycle time.

seeing this post..

e2e.ti.com/.../1157583

Wolfgang said that..

"the problem with the GPMC is the internal bus arbitration time. If you use single byte reads, you won't get any further."

Now, my question is

1. the internal bus arbitration can disturb the GPMC access ?

2. Using EDMA can shorten the cycle2cycle ?

3. Asynchronous Multiple(Page Mode) Read can improve the GPMC access time ?

4. Any ideas, suggestions are welcome.

Regards,

Takeshi Matsuzaki