Hello, I experience that PCMD3180 registers are not retained when returning from software sleep mode.

The hardware sleep mode works fine (SHDNZ pin), configuration retention is not expected in that case obviously.

But I want to save on wakeup time, therefore I'd like to use software sleep mode and expect the settings to be retained.

I follow instructions of the datasheet (SBASA14 –MAY 2020) section 8.2.1.2 points 4 and 5.

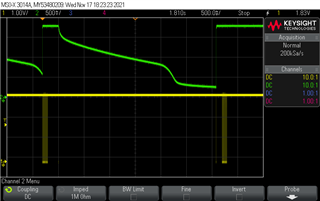

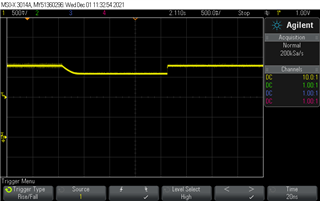

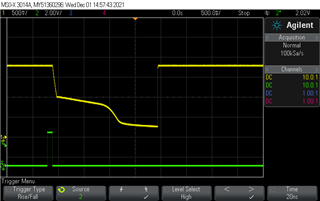

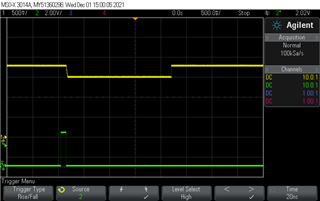

SHDNZ not touched at all, just the sleep register P0_R2 is written. It is confirmed by P0_R119 that sleep mode occurs. Current consumption also confirms this.

On wakeup, my application does not work.

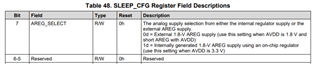

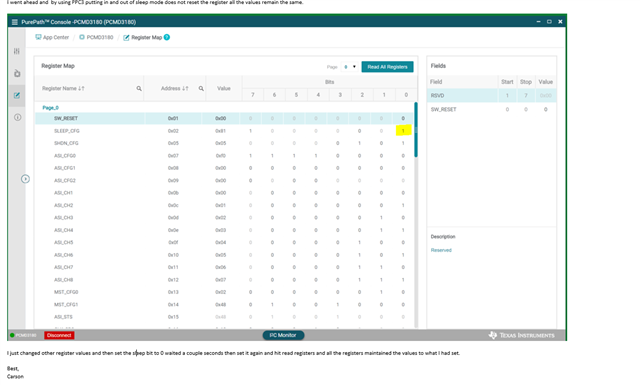

If reading back the registers, I see defaults. For instance, register 0x07 holds value 0x30, although was value 0x40 just before sleeping. I see default for other registers too.

I have tried to keep my MCU completely up and running during the SW sleep mode, to be completely sure that no power loss occurs to PCMD3180.

But I experience the same, if SW sleep is longer than ~2s, registers fall back to defaults.

I expect retention based on section 7.4.2 (Sleep Mode or Software Shutdown)

"""In sleep mode or software shutdown mode, the device consumes very low quiescent current from the AVDD

supply and, at the same time, allows the I2C or SPI communication to wake the device for active operation.

The device can also enter sleep mode when the host device sets the SLEEP_ENZ, P0_R2_D0 bit to 1'b0. If the

SLEEP_ENZ bit is asserted low when the device is in active mode, the device ramps down the volume on the

record data, powers down the analog and digital blocks, and enters sleep mode. However, the device still

continues to retain the last programmed value of the device configuration registers and programmable

coefficients."""

Do you have an idea what can be the case here? Shall I do any special configuration for the retention of registers?