hello,

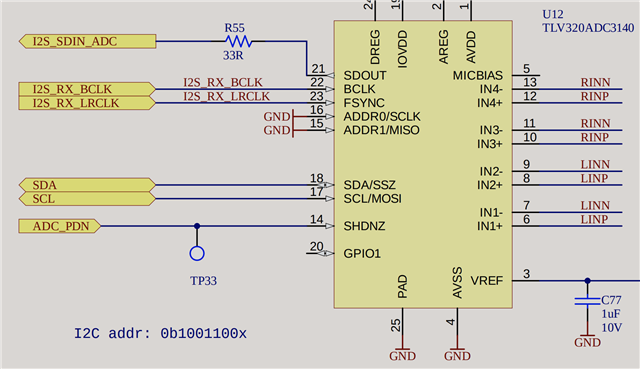

we have a layout looking like this:

running in an embedded system (no linux). we configure the adc like this:

// wake up device

TLV320WriteRegister(TLV320_SLEEP_CFG, TLV320_SLEEP_CFG_AREG_SELECT | TLV320_SLEEP_CFG_WAKE);

// wait for at least 1 ms to allow the device to complete the internal wake-up sequence

Cy_SysLib_Delay(1);

// set up asi i2s mode

TLV320WriteRegister(TLV320_ASI_CFG0, (TLV320_ASI_CFG0_FORMAT_I2S |

TLV320_ASI_CFG0_FORMAT_WLEN_32));

// set up channels

TLV320WriteRegister(TLV320_CH1_CFG0, TLV320_CH_CFG0_LINE_INPUT | TLV320_CH_CFG0_IMP_10);

TLV320WriteRegister(TLV320_CH2_CFG0, TLV320_CH_CFG0_LINE_INPUT | TLV320_CH_CFG0_IMP_10);

TLV320WriteRegister(TLV320_CH3_CFG0, TLV320_CH_CFG0_LINE_INPUT | TLV320_CH_CFG0_IMP_10);

TLV320WriteRegister(TLV320_CH4_CFG0, TLV320_CH_CFG0_LINE_INPUT | TLV320_CH_CFG0_IMP_10);

TLV320WriteRegister(TLV320_DSP_CFG0, (TLV320_DSP_CFG0_CH_SUM_2_CHAN |

TLV320_DSP_CFG0_CH_HPF_12HZ));

TLV320WriteRegister(TLV320_DSP_CFG1, TLV320_DSP_CFG1_BIQUADS_DISABLE);

TLV320WriteRegister(TLV320_ASI_CH2, TLV320_ASI_CH2_SLOT_2);

TLV320WriteRegister(TLV320_ASI_CH3, TLV320_ASI_CH3_SLOT_1);

TLV320WriteRegister(TLV320_GPIO_CFG0, TLV320_GPIO_CFG0_GPIO1_DIS);

// enable input channels

TLV320WriteRegister(TLV320_IN_CH_EN, (TLV320_IN_CH_EN_CH1_EN |

TLV320_IN_CH_EN_CH2_EN |

TLV320_IN_CH_EN_CH3_EN |

TLV320_IN_CH_EN_CH4_EN));

// enable output channels

TLV320WriteRegister(TLV320_ASI_OUT_CH_EN, (TLV320_ASI_OUT_CH_EN_CH1_EN |

TLV320_ASI_OUT_CH_EN_CH3_EN));

// power up adc

TLV320WriteRegister(TLV320_PWR_CFG, (TLV320_PWR_CFG_ADC_EN |

TLV320_PWR_CFG_PLL_EN |

TLV320_PWR_CFG_DYN_CH_PUPD_EN |

TLV320_PWR_CFG_DYN_CH_1_4));

where the defines are:

#define TLV320_PAGE_CFG 0x00 #define TLV320_SW_RESET 0x01 #define TLV320_SLEEP_CFG 0x02 #define TLV320_SLEEP_CFG_AREG_SELECT 0x80 #define TLV320_SLEEP_CFG_WAKE 0x01 #define TLV320_SHDN_CFG 0x05 #define TLV320_ASI_CFG0 0x07 #define TLV320_ASI_CFG0_FORMAT_I2S 0x40 #define TLV320_ASI_CFG0_FORMAT_WLEN_32 0x30 #define TLV320_ASI_CH2 0x0c #define TLV320_ASI_CH2_SLOT_2 0x02 #define TLV320_ASI_CH3 0x0d #define TLV320_ASI_CH3_SLOT_1 0x01 #define TLV320_GPIO_CFG0 0x21 #define TLV320_GPIO_CFG0_GPIO1_DIS 0x00 #define TLV320_CH1_CFG0 0x3c #define TLV320_CH2_CFG0 0x41 #define TLV320_CH3_CFG0 0x46 #define TLV320_CH4_CFG0 0x4b #define TLV320_CH_CFG0_LINE_INPUT 0x80 #define TLV320_CH_CFG0_IMP_10 0x04 #define TLV320_DSP_CFG0 0x6b #define TLV320_DSP_CFG0_CH_SUM_2_CHAN 0x04 #define TLV320_DSP_CFG0_CH_HPF_12HZ 0x01 #define TLV320_DSP_CFG1 0x6c #define TLV320_DSP_CFG1_BIQUADS_DISABLE 0x00 #define TLV320_IN_CH_EN 0x73 #define TLV320_IN_CH_EN_CH1_EN 0x80 #define TLV320_IN_CH_EN_CH2_EN 0x40 #define TLV320_IN_CH_EN_CH3_EN 0x20 #define TLV320_IN_CH_EN_CH4_EN 0x10 #define TLV320_ASI_OUT_CH_EN 0x74 #define TLV320_ASI_OUT_CH_EN_CH1_EN 0x80 #define TLV320_ASI_OUT_CH_EN_CH2_EN 0x40 #define TLV320_ASI_OUT_CH_EN_CH3_EN 0x20 #define TLV320_ASI_OUT_CH_EN_CH4_EN 0x10 #define TLV320_PWR_CFG 0x75 #define TLV320_PWR_CFG_ADC_EN 0x40 #define TLV320_PWR_CFG_PLL_EN 0x20 #define TLV320_PWR_CFG_DYN_CH_PUPD_EN 0x10 #define TLV320_PWR_CFG_DYN_CH_1_4 0x04

we have tried a lot of different things but the right channel is always silent (only zeros are sent out on i2s).

any suggestions on what the issue might be?